Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

281 - 300 / 480

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

半導体装置の製造方法

【課題】異なる動作電圧のトランジスタ群を同一半導体基板に形成し、高電圧動作のトランジスタ群のゲート電極の低抵抗化を可能にし、低動作電圧のトランジスタ群の金属ゲート電極を形成するための導電膜の残査発生をなくすことを可能にする。

【解決手段】半導体基板11に、高動作電圧の第1トランジスタ群と、低動作電圧の第2トランジスタ群とを有し、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13、第1ゲート電極15、シリサイド層とが順に積層され、第2トランジスタ群は、半導体基板11上のダミーゲート18を除去してなるゲート形成溝42内に、第2ゲート絶縁膜と第2ゲート電極を有する半導体装置の製造方法において、第1ゲート電極15をダミーゲート電極16よりも低く形成してから上記シリサイド層を形成し、それらを被覆する層間絶縁膜を形成して表面を平坦化してから、ゲート形成溝を形成する。

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧が低く、トランジスタ間でしきい値電圧のばらつきの無いトランジスタを含む半導体装置を提供する。

【解決手段】nチャネルトランジスタとpチャネルトランジスタとを含む相補型の半導体装置において、nチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)とシリコン(Si)からなる第1化合物層を含む第1メタルゲート電極を備え、pチャネルトランジスタは、ゲート絶縁膜と、ゲート絶縁膜上に形成された、第1金属(M1)と第2金属(M2)とシリコン(Si)からなる第2化合物層を含む第2メタルゲート電極を備え、第1化合物層の組成が、組成式:M1Six(1≦x)で表され、第2化合物層の組成が、組成式:M1M2Siy(0<y≦0.5)で表される。

(もっと読む)

半導体装置製造用基板及びその作製方法

【課題】電気的特性の向上した半導体装置を製造することが可能な半導体装置製造用基板を提供する。

【解決手段】単結晶半導体基板の一表面上にシリコンと酸素とを組成に含む絶縁膜及びシリコンと窒素とを組成に含む絶縁膜を順に積層形成し、単結晶半導体基板に分離層を形成し、シリコンと酸素とを組成に含む絶縁膜にハロゲンイオンを照射して該シリコンと酸素とを組成に含む絶縁膜にハロゲンを含ませた後、シリコンと窒素とを組成に含む絶縁膜上に絶縁膜を形成する。半導体基板及び支持基板を、半導体基板側から順に積層されたシリコンと酸素とを組成に含む絶縁膜、シリコンと窒素とを組成に含む絶縁膜、及び絶縁膜を間に挟んで重ね合わせて接合し、分離層を境として半導体基板の一部を分離させる。

(もっと読む)

SOI基板、半導体装置、SOI基板の作製方法、半導体装置の作製方法、及び半導体装置を用いた表示装置

【課題】基板とSOI層との貼り合わせにおいて、別途装置を用いることなく、容易で精度高い貼り合わせを行うことができるSOI基板、さらには該SOI基板を用いた半導体装置を提供することを課題とする。

【解決手段】基板100の上面の一部に凹部を形成し、該凹部に接合層104を介してSOI層105を貼り合わせた構成とする。予め設けられた凹部に合わせてSOI層105を貼り合わせることができるため、別途装置を用いずに容易に精度の高い貼り合わせを行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】MOS構造の半導体装置において、ゲート電極をイオン注入のチャネリングに対して強い構造とする。

【解決手段】半導体基板上でゲート絶縁膜の上に半導体材料を堆積してゲート電極を形成する。このゲート電極の表面または内部に非晶質層を形成する。その後、ゲートサイドウォールを形成し、ゲート電極およびサイドウォールをマスクとして半導体基板に不純物をイオン注入し、ソース/ドレインを形成する。非晶質層としては、窒素を1×1020〜1×1022/cm3個含む層を形成する。これを、熱処理に対する不純物析出抑制層とし、イオン注入に対するチャネリング防止層とする。

(もっと読む)

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

半導体装置及び当該半導体装置を具備する電子機器

【課題】チャネルドープまたはチャネル領域を微細加工することなく、容易にしきい値電圧の制御が可能なMOSトランジスタを具備する半導体装置を提供することを課題とする。

【解決手段】MOSトランジスタにおいて、ソース領域及びドレイン領域と、ソース領域及びドレイン領域とは逆極性の不純物元素を添加してチャネル領域に隣接して形成した不純物領域と、でPN接合ダイオードを形成する。そして、不純物領域の不純物濃度の範囲は、ソース領域及びドレイン領域と、不純物領域と、がPN接合ダイオードを形成できる濃度範囲で添加されているものとする。

(もっと読む)

半導体装置

【課題】半導体装置において、回路群の中で高速動作、低電圧動作を求められる回路と、高電圧印加時の十分な信頼性が求められる回路とを一体形成するための構成および作製方法を提供することを目的とする。

【解決手段】半導体装置において、同一基板上に単結晶半導体基板より分離、接合された膜厚の異なる単結晶半導体層を含む複数種のトランジスタを有する。高速動作を求められるトランジスタの単結晶半導体層を、電圧に対して高い耐圧性を求められるトランジスタの単結晶半導体層より薄膜化し、単結晶半導体層の膜厚を薄くする。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

デュアルゲートを有するCMOS型半導体装置形成方法

【課題】デュアルゲートを有するCMOS半導体装置形成方法を提供する。

【解決手段】本発明では、素子分離が形成された基板全面に第1ゲート絶縁膜と第1金属含有膜を順次にスタックする。第2不純物型トランジスタ領域で第1金属含有膜と第1ゲート絶縁膜を除去する。第2不純物型トランジスタ領域に第2ゲート絶縁膜と第2金属含有膜をスタックする。第1及び第2金属含有膜をパターニングして第1及び第2不純物型トランジスタ領域に各々第1又は第2ゲート電極を形成する。この時、第1不純物型トランジスタ領域の不純物型がP型であれば、第1金属含有膜のフェルミ準位はP型不純物で高濃度ドーピングされたシリコンの平衡バンド準位と近接したエネルギー準位を有するようにする。

(もっと読む)

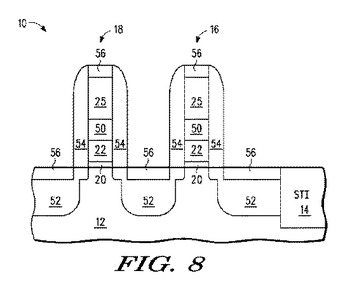

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコンより比誘電率の高い酸化物から構成されるゲート絶縁膜上に、金属から構成されるゲート電極を備えたpチャネル型MOSトランジスタおよびnチャネル型MOSトランジスタにおいて、それぞれのしきい値電圧を低減する。

【解決手段】pチャネル型MOSトランジスタQpおよびnチャネル型MOSトランジスタQnのゲート絶縁膜GIが酸化ハフニウムから構成され、pチャネル型MOSトランジスタQpのゲート電極GEPがルテニウムから構成され、nチャネル型MOSトランジスタQnのゲート電極GENがルテニウムを母材としたハフニウムを含む合金から構成されている。

(もっと読む)

半導体装置及びその製造方法

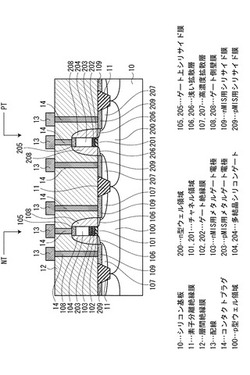

【課題】第1のMISトランジスタと第2のMISトランジスタとで相異なる絶縁材料からなるゲート絶縁膜を精度良く実現する。

【解決手段】N型MISトランジスタNTrは、半導体基板100における第1の活性領域100a上に形成された第1のゲート絶縁膜105aと、第1のゲート絶縁膜上に形成された第1のゲート電極108aとを備え、P型MISトランジスタPTrは、半導体基板における第2の活性領域100b上に形成され、第1のゲート絶縁膜とは異なる絶縁材料からなる第2のゲート絶縁膜103bと、第2のゲート絶縁膜上に形成された第2のゲート電極108bとを備え、第1のゲート電極と第2のゲート電極とは、素子分離領域上において、上部領域が互いに電気的に接続されていると共に、下部領域が互いに第1のゲート絶縁膜と同じ絶縁材料からなる側壁絶縁膜105xyを挟んで分離されている。

(もっと読む)

半導体装置

【課題】ポリシリコン/メタル積層電極構造のポリシリコン/メタル界面における界面抵抗を低減し、動作速度の低下を防止する。

【解決手段】半導体基板100と、領域N1にチャネル領域102を挟むように形成された拡散層103と、ゲート絶縁膜104と、金属膜105a、105b及びn型ポリシリコン膜105cを含むゲート電極105と、を有するnチャネルMISFETと、領域P1にチャネル領域202を挟むように形成されボロンをドーパントして含む拡散層203と、ゲート絶縁膜204と、金属膜205a〜c及び窒素を含む金属膜205cとの界面部におけるボロン濃度が5E19cm−3以下であるn型ポリシリコン膜205dを含むゲート電極205と、を有するpチャネルMISFETと、を備える。

(もっと読む)

高kゲート誘電体を有するCMOS回路

【課題】 高k含有ゲート誘電体を有するCMOS構造体、及び、ゲート誘電体を酸素に曝露することによって閾値電圧を調整する方法を提供する。

【解決手段】 第1の型のFETが、酸化物部分と窒化物部分とを有するライナを含む、CMOS構造体が開示される。この窒化物部分は、ライナのエッジ・セグメントを形成している。これらの窒化物部分は、酸素が第1の型のFETの高k誘電体に通るのを防止することができる。CMOS構造体の第2の型のFETデバイスは、窒化物部分を持たないライナを有する。その結果、酸素曝露により、第1の型のFETの閾値に影響を及ぼすことなく、第2の型のFETの閾値電圧をシフトさせることができる。この開示はまた、異なる型のFETデバイスが、互いに独立して設定された閾値を有する、CMOS構造体を製造する方法も教示する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明はフィントランジスタを含む半導体素子及びその製造方法に関する。

【解決手段】半導体素子は、素子分離構造を備えた半導体基板に画成されたフィン型活性領域と、フィン型活性領域の上部に形成されたリセスと、フィン型活性領域の上部に形成され、前記リセスを埋め込むシリコンゲルマニウム層を含むゲート電極とを含む。

(もっと読む)

半導体デバイスにおける分離層の形成

半導体デバイス101が半導体層107により形成される。半導体層107の上方に第1のゲート誘電体層109が形成される。第1のゲート誘電体109の上方に第1の導体層111が形成される。第1の導体層の上方に第1の分離層113が形成される。第1のメサ201および第2のメサ203を分離するために半導体層107にトレンチ205が形成される。トレンチ205は第1の導体層111の上面を越える高さまで絶縁材料401で充填される。第2のメサ203から第1の導体層111が除去される。第1のメサ203の第1の分離層113の上方および第2のメサ203の上方に第2の導体層703が形成される。平坦化エッチングによって第1のメサ201の上方から第2の導体層703が除去される。第1のメサ201において第1の種類の第1のトランジスタ1201が形成され第2のメサ203において第2の種類の第2のトランジスタ1203が形成される。  (もっと読む)

(もっと読む)

281 - 300 / 480

[ Back to top ]