Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

261 - 280 / 480

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体装置、及びその作製方法

【課題】半導体基板(SOI基板)の大面積化を課題とする。また、効率のよい半導体基板の作製方法を提案することを課題とする。また、上記の半導体基板の特性を向上することを課題とする。また、上記の半導体基板を用いた半導体装置及び電子機器を提供することを課題とする。

【解決手段】半導体基板(SOI基板)の大面積化及び作製効率の向上を図るために、複数の単結晶半導体基板を同時に処理して、半導体基板を作製する。具体的には、複数の単結晶半導体基板の処理を同時に可能とするトレイを用いて、一連の工程を行う。また、ベース基板に形成した単結晶半導体層に対してエッチング処理又はエッチバック処理を施すことにより、単結晶半導体層に存在する損傷領域を除去すると共に、隣接する単結晶半導体層の間隙におけるベース基板の表面の一部を除去して、ベース基板に凹部を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】均一な形状・特性を有するFinFETのゲート電極を安定して形成する。また、FinFETを構成するゲート電極の剥離やゲート絶縁膜の絶縁性の劣化を防止することにより、安定で均一な特性を有するFinFETを備えた半導体装置を提供する。

【解決手段】(9)全面にポリシリコン膜を形成する工程と、(10)マスクパターンをストッパに用いて、ポリシリコン膜にCMP処理を行う工程、(11)全面に金属膜を形成する工程、(12)ポリシリコン膜の少なくとも一部と、金属膜の少なくとも一部とを反応させて、金属のシリサイド化を行うことによりゲート電極を形成する工程、ゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜が大気やメタル電極のエッチング液等に曝されて劣化することなく、仕事関数の異なるnMOS、pMOSに適したメタルゲートMISFETを含む半導体装置の製造方法を提供する。

【解決手段】 メタル電極を有するn型MISトランジスタ及びp型MISトランジスタを備えた半導体装置の製造方法であって、単結晶シリコン基板100上に設けられたゲート絶縁膜102と、ゲート絶縁膜102上に設けられた第一の金属膜103、第二の金属膜104、第三の金属膜105、導電層106を備えたゲート電極108とを備えた構造であって、熱工程によって第二の金属膜104の構成元素を第一の金属膜103を通してゲート絶縁膜102中へ拡散させることによって、n型MISトランジスタ及びp型MISトランジスタそれぞれに適した仕事関数に変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

半導体装置

【課題】電流駆動能力が高いMOSFETを備えた半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2の表面にNMOS3を形成し、NMOS3のチャネル領域7の直上域に、内部に圧縮応力を有する圧縮応力膜8を設け、シリコン基板2上における少なくともチャネル領域7の直上域の周囲に、内部に引張応力を有する引張応力膜9を設ける。

(もっと読む)

半導体デバイスにおいてゲート電極高を調整するための方法

高エネルギー注入プロセス(203)中に、高度な半導体デバイス(200)のゲート電極構造(252)上に注入ブロック材料(258)を設けることによって、トランジスタ(250A,250B)のチャネル領域(255)に対する必要な遮蔽効果を得ることができる。後の製造段階において、層間絶縁材料(210)の堆積時のプロセス条件を向上させるために、注入ブロック部分(258)が除去されてゲート電極高さ(253H)が所望の高さに低減され、これにより、高密度のデバイス領域であっても、層間絶縁材料(210)内にボイドなどの不規則性が形成されるリスクを大幅に低減することができる。  (もっと読む)

(もっと読む)

nチャネルMOSトランジスタおよびその製造方法、半導体装置

【課題】ゲートファーストプロセスで形成できる、金属化合物をゲート電極パターンとして使うnチャネルMOSトランジスタにおいて、pチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物に対し、前記nチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物の仕事関数差を増大させる。

【解決手段】nチャネルMOSトランジスタは、p型シリコン活性領域上にゲート絶縁膜を介して形成された導電性金属窒化物よりなるゲート電極パターンと、前記p型シリコン活性領域中、前記ゲート電極パターンの一方および他方の側にそれぞれ形成されたn型のソースおよびドレイン領域と、を含み、前記導電性金属窒化物は、SiおよびV族元素を含む。

(もっと読む)

半導体装置の製造方法

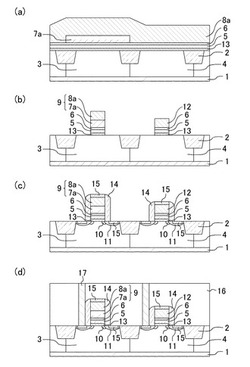

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

固体撮像素子およびその製造方法

【課題】固体撮像素子において、画像信号に対するノイズを抑制しながら、周辺回路形成領域のみならず画素形成領域においてもさらに素子間分離領域を微細化する。

【解決手段】N型のシリコン基板から成る同一の半導体基板10に、フォトダイオード2を含む複数の画素セルが2次元状に形成された画素形成領域4と、周辺回路形成領域20とが形成されている。画素形成領域4は、フォトダイオード2およびアンプトランジスタ8を含み、周辺回路形成領域20はN型チャネルトランジスタ26を含む。周辺回路形成領域20の素子分離層21はSTI構造により素子間を分離する。画素形成領域4においては、半導体基板上に突出した素子分離層12と基板内に埋め込まれた素子分離領域11とが、素子間を分離する。素子分離層12は、半導体基板10表面に形成された酸化膜を選択的に除去することにより形成される。

(もっと読む)

厚さが減少した半導体素子、これを採用する電子製品及びその製造方法

【課題】厚さが減少した半導体素子、これを採用する電子製品及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は第1及び第2活性領域を有する半導体基板を準備する工程を含む。前記第1活性領域に第1ゲートパターン及び第1不純物領域を含む第1トランジスタを形成する。前記第2活性領域に第2ゲートパターン及び第2不純物領域を含む第2トランジスタを形成する。前記第1トランジスタ上に第1導電性パターンを形成する。前記第1導電性パターンの少なくとも一部と前記第2ゲートパターンの少なくとも一部は前記半導体基板の上部表面から同一距離に配置される。前記第1導電性パターンは前記第2ゲートパターンを形成する間に形成される。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】ホウ素(B)のゲート絶縁膜の突き抜けや金属シリサイド膜による不純物の吸収によって生じるポリシリコン膜中の不純物の空乏化を防止する。

【解決手段】半導体装置100は、ゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14とを備える。ゲート電極14は、ドープドポリシリコン膜21a、21b、21cと、金属シリサイド膜22aとを備えている。ドープドポリシリコン膜21a、21cは、第1の不純物を含んでおり、ドープドポリシリコン膜21bは、反対の導電型を有する第2の不純物を含んでいる。これにより、ポリシリコン中の不純物の拡散工程やその後の熱負荷工程において、第2のドープドポリシリコン膜中の不純物の過度な拡散が抑制され、金属シリサイド膜が不純物を吸収することによるポリシリコン膜中の不純物の空乏化が防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETとpチャネル型MISFETで異なる金属膜を使用する場合であっても、両方のゲート電極を同時に加工できる技術を提供する。

【解決手段】pチャネル型MISFET形成領域に改質膜11を形成している。改質膜11は、ポリシリコン膜9にリンを導入することにより形成されている。この改質膜11は、ポリシリコン膜9よりもエッチング速度が速くなる性質がある。このことから、pチャネル型MISFET形成領域において、改質膜11とポリシリコン膜9をすべてエッチングする際、nチャネル型MISFET形成領域においては、ポリシリコン膜9がすべてエッチングされずに一部が残存する。これにより、pチャネル型MISFET形成領域に形成されている膜の総膜厚と、nチャネル型MISFET形成領域に形成されている膜の総膜厚の差が緩和される。

(もっと読む)

半導体装置の作製方法

【課題】生産コストを削減することができる半導体装置の作製方法の提案を課題とする。

【解決手段】ボンド基板の下に容器を配置した後、ボンド基板を劈開させることでボンド基板から形成される複数の第1の半導体膜を、容器に載置し、複数の第1の半導体膜を容器から拾い上げて、複数の第1の半導体膜どうしが離隔するようにベース基板に貼り、複数の第1の半導体膜をエッチングすることで、複数の第2の半導体膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに隣接するシリコンエピタキシャル層同士のショートを防止する。

【解決手段】活性領域13の露出面をドライエッチング又はウェットエッチングで掘り下げることにより、活性領域13の露出面には凹部13aが形成される。これにより、素子分離領域12を構成するフィールド酸化膜12の側面部分12aが露出し、凹部13aの周囲がフィールド酸化膜の側面部分12aで囲まれた状態となる。その後、凹部13aが形成された活性領域13の露出面にシリコンエピタキシャル層19を形成する。ここで、活性領域の露出面は掘り下げられており、活性領域13の幅方向の両端はフィールド酸化膜による壁で囲われていることから、シリコンエピタキシャル層19の横方向への成長を抑制することができ、互いに隣接するシリコンエピタキシャル層19、19間のショートを防止することができる。

(もっと読む)

MOSトランジスタの製造方法、および、これにより製造されたMOSトランジスタ

【課題】MOSトランジスタの製造方法、およびこれにより製造されたMOSトランジスタを提供する。

【解決手段】半導体基板100上にゲートパターン120を形成する工程と、前記ゲートパターンの側壁を覆うスペーサ134を形成する工程と、を含み、前記ゲートパターンを形成する工程は、順に積層されるゲート電極112a、キャッピング膜パターン118、を備えるように形成し、前記キャッピング膜パターンは、順に積層される下部キャッピング膜パターン114b、上部キャッピング膜パターン116a、を備えるように形成し、前記下部キャッピング膜パターンは前記上部キャッピング膜パターンよりも小さい幅を有するように形成する、ことを含む。

(もっと読む)

半導体装置の製造方法

【課題】異なる動作電圧のトランジスタ群を同一半導体基板に形成し、高電圧動作のトランジスタ群のゲート電極の低抵抗化を可能にし、低動作電圧のトランジスタ群の金属ゲート電極を形成するための導電膜の残査発生をなくすことを可能にする。

【解決手段】半導体基板11に、高動作電圧の第1トランジスタ群と、低動作電圧の第2トランジスタ群とを有し、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13、第1ゲート電極15、シリサイド層とが順に積層され、第2トランジスタ群は、半導体基板11上のダミーゲート18を除去してなるゲート形成溝42内に、第2ゲート絶縁膜と第2ゲート電極を有する半導体装置の製造方法において、第1ゲート電極15をダミーゲート電極16よりも低く形成してから上記シリサイド層を形成し、それらを被覆する層間絶縁膜を形成して表面を平坦化してから、ゲート形成溝を形成する。

(もっと読む)

261 - 280 / 480

[ Back to top ]