Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

421 - 440 / 480

多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタ、これを採用するCMOS集積回路素子及びその製造方法

【課題】多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタが提供される。

【解決手段】MOSトランジスタは半導体基板及び前記半導体基板上に配置された中心ゲート電極を具備する。前記中心ゲート電極は金属窒化物からなる。前記中心ゲート電極の両側壁上にそれぞれソース側ゲート電極及びドレイン側ゲート電極が提供される。前記ソース/ドレイン側ゲート電極は窒素よりも小さい電気陰性度を有する第1不純物または窒素よりも大きい電気陰性度を有する第2不純物を含むドープ金属窒化物からなる。前記MOSトランジスタを採用するCMOS集積回路素子及びその製造方法も提供される。

(もっと読む)

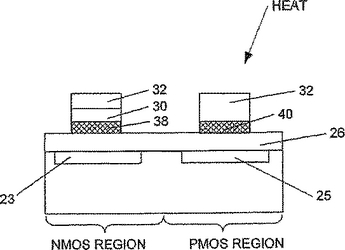

自己整合され積極的にスケーリングされたCMOSデバイスにおけるゲート電極の金属/金属窒化物二重層のCMOS構造体及び半導体構造体

【課題】 低仕事関数金属の不適切な熱安定性のために、nFET仕事関数とpFET仕事関数との両方を適正にするために用いることができるゲート・スタックを有するCMOS構造体を提供すること。

【解決手段】 本発明は、半導体基板の1つの領域上に配置された少なくとも1つのnMOSデバイスと、半導体基板の別の領域上に配置された少なくとも1つのpMOSデバイスとを含む、CMOS構造体に向けられる。本発明によれば、少なくとも1つのnMOSデバイスは、ゲート誘電体と、4.2eV未満の仕事関数を有する低仕事関数の元素状金属と、その場金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを含み、少なくとも1つのpMOSデバイスは、ゲート誘電体と、4.9eVより大きい仕事関数を有する高仕事関数の元素状金属と、金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを有する。本発明はまた、こうしたCMOS構造体を製造する方法も提供する。

(もっと読む)

デュアルメタルゲート電極を有するCMOSデバイスの製造方法

金属エッチング工程においてゲート誘電体(26)が露出することを防止するために、処理の間、メタルゲート(30)とゲート誘電体(26)との間の超薄窒化アルミニウム(AlNx)バッファ層(28)を使用する、デュアルメタルゲートCMOS構造

を構築する方法。不必要なゲートメタルをエッチング除去した後、CMOS構造は熱処理される。熱処理の間に、メタルゲート(30)との反応を通じてバッファ層(28)は完全に消費され、新らしいメタル合金(38,40)が形成される。その結果、実効酸化膜厚は最小限しか増加しない。バッファ層(28)およびゲートメタル(30)は、元のゲートメタルの仕事関数が熱処理工程の結果変化するため、メタル/誘電体界面の仕事関数の決定に重要な役割を果たす。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を大幅に増加させることなく、P型MOSFETとN型MOSFETとで異なる仕事関数を有する金属ゲート電極を形成する。

【解決手段】N型MOSトランジスタとP型MOSトランジスタとが形成された半導体装置であって、N型MOSトランジスタのゲート電極107nは、ゲート絶縁膜104に接するタングステン膜105nを具備し、P型MOSトランジスタのゲート電極107pは、ゲート絶縁膜104に接するタングステン膜105pを具備し、タングステン膜105nに含有される炭素の濃度が、タングステン膜105pに含有される炭素の濃度よりも低いことを特徴とする。

(もっと読む)

多層ゲート構造を備える半導体素子及びそれの製造方法

【課題】半導体基板と半導体基板上に形成されたドープされた導電膜を含む半導体素子を提供する。

【解決手段】拡散バリヤ膜がドープされた導電膜上に形成される。拡散バリヤ膜は、非晶質半導体物質を含む。オーミックコンタクト膜が拡散バリヤ膜上に形成される。金属バリヤ膜がオーミックコンタクト膜上に形成される。金属膜が金属バリヤ膜上に形成される。これにより、界面抵抗を所望の範囲内に維持できながら、オーミックコンタクト膜下部の導電体にドープされた不純物が外部に拡散することを効果的に防止できて、多層構造を採用した半導体素子の反転キャパシタンス特性などを向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 活性領域とタングステンプラグとの接触面積の低下を防止する。

【解決手段】 シリコン基板1にSTI2を形成し、活性領域3を区画形成する。ゲート電極4aを形成した後に、活性領域3のコンタクトホール5を形成する領域の表面を上に凸の滑らかな表面となるようにRIE加工する。層間絶縁膜10にコンタクトホール5を形成する際に、パターンずれが発生してもコンタクトプラグ13との接触面積の低下を防止できる。設計ルールの縮小化に伴う不具合を回避することができる。

(もっと読む)

デュアルメタルゲート構造を形成するためのプロセス

半導体デバイス(10)は、Pチャンネルゲート層(38)を有し、Pチャンネルゲート層(38)は、第1メタル(18)と、同第1メタル(18)上に第2メタル(20)とを備えている。また、半導体デバイス(10)は、Nチャンネルゲート層(40)を有し、Nチャンネルゲート層(40)は、ゲート誘電体(14)と直接接する第2メタル(18)を備えている。Nチャンネルゲート層(40)、及びPチャンネルゲート層(38)の一部には、ドライエッチングによるエッチング処理が施される。Pチャンネルゲート層(38)は、ウェットエッチングにより仕上げられる。ウェットエッチングは、ゲート誘電体(14)と第2メタルとの両方に対して極めて選択的である。そのため、Nチャンネルトランジスタは、Pチャンネルゲート層(38)のエッチング仕上げによる影響を受けない。  (もっと読む)

(もっと読む)

半導体装置及びそれを用いた電子機器

【課題】高機能化、多機能化及び付加価値化を実現した半導体装置の提供を課題とする。

【解決手段】基板上に、正確な周波数の信号を出力する回路(フェーズ・ロックド・ループ回路、PLL回路)を設けた半導体装置を提供する。PLL回路は、供給される信号を基に、一定の倍率の周波数の信号を出力する回路である。PLL回路は、位相比較器、ループフィルタ、電圧制御発振器及び分周器を含む。基板上にPLL回路を設けることにより、高機能化、多機能化及び高付加価値化を実現することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗で耐熱性を有し、閾値変動もないCMOSデバイスを提案する。

【解決手段】本発明の例に関わる半導体装置は、N型半導体層3と、N型半導体層3上に形成される第1ゲート絶縁層10と、第1ゲート絶縁層10上に形成され、金属の炭素化合物を含む第1ゲート電極12とを有するPチャネルMISトランジスタ、及び、P型半導体層2と、P型半導体層2上に形成される第2ゲート絶縁層10と、第2ゲート絶縁層10上に形成される第2ゲート電極11とを有するNチャネルMISトランジスタを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 半導体基板に加わるダメージが小さい半導体装置の製造方法を提供する。

【解決手段】 本発明に係る半導体装置の製造方法は、半導体基板1に素子分離膜2を形成することにより、素子領域を他の領域から分離する工程と、素子領域に位置する半導体基板1上に、ゲート絶縁膜3を形成する工程と、素子分離膜2上及びゲート絶縁膜3上に、不純物が導入された第1のポリシリコン膜41を形成する工程と、第1のポリシリコン膜41上に、第2のポリシリコン膜42を形成する工程と、第1のポリシリコン膜41及び第2のポリシリコン膜42をパターニングすることにより、ゲート絶縁膜3上に位置するゲート電極4を形成する工程とを具備する。

(もっと読む)

半導体装置

【課題】 ゲート電極に多結晶Si/金属積層構造を用いつつ、多結晶Si/金属界面の空乏化を抑制することを目的とする。

【解決手段】

ゲート電極が上層に多結晶Si層6、下層に金属層(TiN層7)の積層構造を成して、かつ上部配線とのコンタクト部分は、上部配線がゲート積層構造の下層金属層まで到達させることで、多結晶Siと下層金属(TiN)に電位差が生じないため、空乏層が伸びることなく、ゲートに印加した電圧と同じだけゲート絶縁膜に電圧が掛かり十分なキャリアがチャネル領域に形成され、駆動電流の向上が得られる。また、ゲート加工が基本的には既存技術をそのまま適用できるため、金属ゲート電極を有する半導体装置の製造及びその技術開発が簡略化される。

(もっと読む)

半導体装置の製造方法

【課題】同一半導体基板上に、半導体素子の要求性能に応じた互いにリセス量の異なる複数の素子分離部を形成することのできる技術を提供する。

【解決手段】半導体基板1をエッチングして活性領域の平面外形を規定する溝4を形成し、さらに溝4の内部を埋め込む絶縁膜5を堆積した後、周辺回路高耐圧系MISの形成領域では活性領域よりも小さい抜きパターンが形成され、メモリセルおよび周辺回路低耐圧系MISの形成領域では活性領域よりも大きい抜きパターンが形成されたレジストパターンをマスクとして活性領域上、ならびにメモリセルおよび周辺回路低耐圧系MISの形成領域の溝4の内部に埋め込まれた絶縁膜5をエッチング、続いて絶縁膜5を研磨して溝4の内部に絶縁膜5を埋め込む。

(もっと読む)

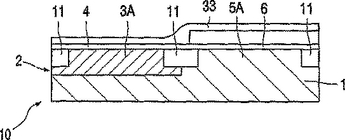

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、基板(1)と半導体本体(2)とを有する半導体装置(10)であって、第一のチャネル領域(3A)と第一の導体を含み且つ誘電体層(4)によりチャネル領域から分離された第一のゲート電極(3B)とを有する第一の(NMOS)FET(3)を備え、そして、第二のチャネル領域(5A)と第一の導体とは異なる第二の導体を含み且つ誘電体層(4)によりチャネル領域(5A)から分離された第二のゲート電極(5B)とを有する第二の(PMOS)FET(5)を備え、第一及び第二のゲート電極(3B、5B)を形成するために、誘電体層(4)が備えられた半導体本体(2)上に第一の導体層(33)が堆積され、導体層(33)は、その後、第一のチャネル領域(3A)外部で除去され、その後、第二の導体層(55)が半導体本体(2)上に堆積され、そして、第一の導体層(33)が堆積される前に、誘電体層(4)上に中間層(6)が堆積される半導体装置の製造方法に関する。この発明によれば、中間層(6)のための材料として誘電体層(4)に対し選択的にエッチング可能な材料が選ばれ、そして、第一の導体層(33)が堆積される前に、第一のチャネル領域(3A)の位置で中間層(6)が除去され、そして、第一の導体層(33)が堆積され、第一のチャネル領域(3A)外部で除去された後に、そして、第二の導体層(55)が堆積される前に、第二のチャネル領域(5A)の位置で中間層(6)が除去される。従って、FETが、簡単な方法で、且つ、それらのゲート誘電体にダメージを与えずに得られる。好ましくは、中間層(6)に対して選択的にエッチング可能なさらなる中間層(8)が中間層(6)上に堆積される。  (もっと読む)

(もっと読む)

CMOSプロセス用金属ゲート・トランジスタ及びその製造方法

半導体装置(100)を形成する方法は、第一領域(104)を備える半導体基板と、第一領域上にゲート誘電体(108)を形成するステップと、ゲート誘電体上に導電性金属酸化物(110)を形成するステップと、導電性金属酸化物上に耐酸化バリア層(111)を形成するステップと、耐酸化バリア層上にキャッピング層(116)を形成するステップとを含む。一実施形態において、導電性金属酸化物はIrO2,MoO2及びRuO2であり、耐酸化バリア層はTiNを含む。  (もっと読む)

(もっと読む)

互いに重ねて堆積させた金属層の積層体中に形成されたゲート電極を含むMOSトランジスタを備える半導体デバイスの製造方法

互いに重ねて堆積させたいくつかの金属層(8,9,13;8,12,13)として形成したゲート電極(15,16)を有するMOSトランジスタを備える半導体デバイスの製造方法。この方法では、シリコン本体(1)に、ゲート誘電体層(7)を備えるシリコン活性領域(4,5)およびこれらの領域を互いに絶縁するフィールド分離領域(6)を形成する。次いで、第1の金属層(8)を堆積させ、活性領域(4)の一部の位置でその層中に局所的に窒素を導入する。次いで、第1の金属層上に第2の金属層(13)を堆積させ、その後それらの金属層中にゲート電極をエッチングする。第1の金属層中に窒素を導入する前に、第1の金属層上に窒素透過性の第3の金属補助層(9)を堆積させる。したがって、その下にあるゲート電極に損傷を与える危険なく、第1の金属層を窒化することができる。金属の仕事関数を実質的に変えることが可能であるとともに、NMOSおよびPMOSを備える半導体デバイスが実現される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 N型ポリメタルゲート電極とP型ポリメタルゲート電極の界面抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板101上にシリコン膜を形成する工程と、シリコン膜の領域PにP型不純物を、領域NにN型不純物をこの順にイオン注入する工程と、シリコン膜上にシリサイド膜106及び金属膜をこの順で形成する工程と、シリコン膜、シリサイド膜106及び金属膜をパターニングして領域PにP型ポリメタルゲート電極を、領域NにN型ポリメタルゲート電極を形成する工程とを備え、P型不純物のイオン注入後、N型不純物のイオン注入前に第1の熱処理を行ってP型不純物を活性化させ領域Pのシリコン膜をポリシリコン膜103Pとし、N型不純物のイオン注入後、第2の熱処理を行い、N型不純物を活性化させ領域Nのシリコン膜をポリシリコン膜103nにすると共にシリサイド膜106に含まれたガスを除去する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 CMOSを基板上に有する半導体集積回路装置において、pMOSトランジスタにおいてSiGe混晶層よりなる圧縮応力発生源を、基板中、前記pMOSトランジスタのチャネル領域に可能な限り近接させて配置し、同時にnMOSトランジスタにおいて、ソース/ドレイン拡散領域の間に充分な距離を確保してリーク電流の発生を抑制する。

【解決手段】 pMOSトランジスタのゲート電極側壁絶縁膜を、HF耐性を有する膜により形成し、pMOSトランジスタの素子領域に前記p型SiGe混晶層がエピタキシャル成長するトレンチを、前記pMOSトランジスタのチャネル領域に近接して形成すると同時に、nMOSトランジスタ領域においては、ゲート電極の側壁絶縁膜の外側にさらに別の側壁絶縁膜を形成し、基板中にイオン注入により形成されるn型ソース/ドレイン領域の間に充分な距離を確保する。

(もっと読む)

CMOSデバイスの自己形成金属シリサイド化ゲート

【課題】 CMOSデバイスの自己形成金属シリサイド化ゲートを提供すること。

【解決手段】 シリサイドが自己形成され(すなわち、別個の金属/シリコン反応ステップを必要とせずに形成され)、シリコン材料のCMP又はエッチ・バックを必要としない、金属シリサイド・ゲートをFETデバイスに形成するためのプロセス。第1のシリコン材料層(3)(ポリシリコン又はアモルファス・シリコン)が、ゲート誘電体(2)の上に形成され、次いで、金属層(4)が第1のシリコン材料層(3)の上に形成され、金属層(4)の上に第2のシリコン材料層(5)が形成される。その後、ソース/ドレイン活性化アニールのような高温(700℃より高い)処理ステップが実施され、このステップは、金属層(4)の金属を第1のシリコン材料層(13)におけるシリコン材料と反応させることにより、ゲート誘電体(2)の上にシリサイド層(30)を形成するのに有効である。第2の高温処理ステップ(ソース/ドレインのシリサイド化のような)を実施することができ、これは第2のシリコン材料層(5)におけるシリコン材料から第2のシリサイド層(50)を形成するのに有効である。シリサイド層の厚さは、高温処理において、第1のシリコン材料層の実質的にすべて及び第2のシリコン材料層の少なくとも一部が、シリサイド材料で置き換えられるような厚さである。従って、完全シリサイド化ゲート構造体を生成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ホウ素及びリンを含むシリコン層を最下層に有するゲート電極の端部の尖りが抑制された半導体装置及びその製造方法を提供する。これによってゲート電流の増加を抑制し、CMOSデバイスのNBTI劣化を抑制する。

【解決手段】 半導体装置10は、シリコン基板11と、シリコン基板11上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成され、ホウ素及びリンを含むポリシリコン層18bを最下層に有するゲート電極17とを備える。ポリシリコン層18b中のホウ素の最大濃度と最小濃度との比が100以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの特性に適応した仕事関数をもつデュアルメタルゲートを備え、トランジスタ特性や信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に、ゲート絶縁膜3および金属層4を形成する。nMOS領域あるいはpMOS領域のいずれか、例えばpMOS領域にバリアメタル層5を形成した後に、全面に導電層6として例えばポリシリコンを成膜する。nMOS領域およびpMOS領域において、ゲート電極形状に加工した後に、熱処理を行う。これにより、nMOS領域では、金属層4と導電層6の合金層7からなる第2ゲート電極G2が形成される。pMOS領域では、バリアメタル層5により金属層4と導電層6との反応が抑制され、積層膜からなる第1ゲート電極G1となる。

(もっと読む)

421 - 440 / 480

[ Back to top ]