Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

381 - 400 / 480

半導体装置のデュアルゲート構造物及びその形成方法

【課題】高誘電膜を含むCMOSトランジスタの形成に適合した構造を有するデュアルゲート構造物及びその形成方法を提供する。

【解決手段】デュアルゲート構造物は、第1及び第2領域が区分される基板と、前記第1領域の基板上に形成され、金属酸化膜、第1仕事関数を有する金属物質からなる第1金属パターン、シリコン拡散防止膜パターン、及びシリコンを含む導電膜パターンが積層された第1ゲート構造物と、前記第2領域の基板上に形成され、金属酸化膜、前記金属物質及びシリコン元素を含み前記第1仕事関数より低い第2仕事関数を有する第2金属パターン、及び前記シリコンを含む導電膜パターンが積層された第2ゲート構造物と、を含む。前記デュアルゲート構造物は各領域に形成されるゲート電極が同一の金属物質からなるので前記金属物質の一部を除去しなくてもよいので前記除去工程の際発生する金属酸化膜の損傷を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト不良を防止しつつ応力膜を用いて効果的にチャネル形成領域に応力を印加することにより、MISFETの駆動力の向上を図る。

【解決手段】半導体基板1上に形成されたMISFETのゲート電極部20n及び20pの側面上には絶縁性のサイドウォールスペーサ9が形成されている。ゲート電極部20n及び20pの高さは、それぞれの側面上に設けられたサイドウォールスペーサ9の上端より低い。MISFET上にゲート電極部20n及び20pを覆うように、チャネル形成領域に応力を発生させる応力膜13が形成されている。応力膜13におけるゲート電極部20n及び20p上に形成されている部分の膜厚が、その他の部分の膜厚よりも厚い。

(もっと読む)

半導体構造およびその形成方法(応力付加膜によりN型MOSFETおよびP型MOSFET双方の性能を向上させる方法および構造)

【課題】p型MOSFETデバイスのチャネル内に圧縮応力をもたらし、n型MOSFETデバイスのチャネル内に引張応力をもたらす応力層が、各々のゲート・スタックに重ねられている、隣接するp型MOSFETデバイスおよびn型MOSFETデバイスを含む構造および製造方法を提供すること。

【解決手段】p型MOSFETデバイスまたはn型MOSFETデバイスのうちの一方が、隣接する他方のデバイスの高さよりも低い高さを有し、2つのデバイスのうちの低い方が、低い方のデバイスに重ねられた応力層内の不連続部すなわち開口部によって境界が画定されている。デバイスを形成するための好ましい一方法では、ゲート・スタック下の基板内に第1のタイプの応力を形成するために、異なる高さを有するゲート・スタック上に単一の応力層が形成され、第2のタイプの応力が低い方のゲート・スタックの下に形成されるように、低い方のゲート・スタックからある距離のところの応力層内に開口部が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高精度でメタルゲート電極の仕事関数を制御することができる、メタルゲート電極を用いたMOS型の半導体装置を提供すること。

【解決手段】半導体基板10と、半導体基板10の主面に絶縁膜16を介して形成されたメタルゲート電極25と、主面にメタルゲート電極を挟んでそれぞれ形成されたソース電極33およびドレイン電極34とを有するMOS型の半導体装置において、メタルゲート電極25は、金属窒化物膜17とその金属窒化物の金属と同じ金属からなる金属膜18との2層構造を形成した後に金属窒化物膜17の窒素を金属膜に固相拡散させることにより形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化及び高速化が可能な半導体装置に必要なNi合金シリサイド層を形成する際に、所望の耐熱性を持つシリサイドを所望の領域に形成できるようにする。

【解決手段】半導体基板100上にゲート電極103A及び103Bを形成した後、半導体基板100におけるゲート電極103Aの両側及びゲート電極103Bの両側にそれぞれソース・ドレイン領域となる高濃度不純物拡散層109A及び109Bを形成する。ゲート電極103A上及び高濃度不純物拡散層109A上に第1のニッケル合金シリサイド層113を形成する。ゲート電極103B上及び高濃度不純物拡散層109B上に第2のニッケル合金シリサイド層117を形成する。ニッケル合金シリサイド層113及び117をそれぞれ形成する工程において、半導体基板100上にニッケル合金膜及びニッケル膜を順次堆積した後に熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲート電極をメタルの凝集なく仕事関数変調により形成する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板100上にゲート絶縁層102を形成する工程と、ゲート絶縁層102上に第1メタル層103を形成する工程と、第1メタル層103上に第2メタル層104を形成する工程と、第2メタル層104上に第2メタル層104よりも高い融点を持つ材料からなるキャップ層105を形成する工程と、熱処理により第2メタル層104内の元素をゲート絶縁層102と第1メタル層103との界面に析出させて析出層107を形成する工程とを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高品質の極薄酸化膜を均一な膜厚で再現性良く形成する。

【解決手段】半導体ウエハ1Aを酸化膜形成室107の熱処理チャンバ120へ導入する工程と、熱処理チャンバ120内のガス雰囲気を窒素によって置換する工程と、第1の温度で、触媒を用いて酸素と水素から水分を合成する工程と、合成した水分を前記酸化炉107の熱処理チャンバ120へ導入して、気化状態を維持したまま、熱処理チャンバ120内の半導体ウエハ1Aの第1主面上に水分を含んだ酸化性雰囲気を形成する工程と、熱処理チャンバ120内の水分を含んだ酸化性雰囲気において、前記第1の温度より高い第2の温度まで半導体ウエハ1Aの主面をランプ加熱して、半導体ウエハ1Aの第1主面上のシリコン表面を熱酸化処理して絶縁膜を形成する工程と、前記工程の後、熱処理チャンバ120内の前記水分を含んだ酸化性雰囲気を窒素によって置換する工程とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】不揮発性メモリを有する半導体集積回路装置の周辺回路のゲート電極の抵抗を低下させる。

【解決手段】2層ゲート電極構造の不揮発性メモリセルと同じゲート電極構造によって周辺回路用のMOSQAのゲート電極GAを構成し、そのゲート電極GAを構成する導体膜4,6間を接続するコンタクトホールSCを、そのゲート電極GAの平面内において活性領域LAと平面的に重なる位置に配置した。

(もっと読む)

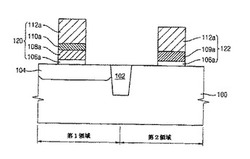

半導体装置およびその製造方法

【課題】 nMISおよびpMIS形成領域の高誘電率ゲート絶縁膜上に設けられたデュアルメタルゲート電極の仕事関数の変化を抑制して、信頼性の高い半導体装置を製造する方法を提供する。

【解決手段】 単結晶シリコン基板100のnMISおよびpMIS形成領域に高誘電率ゲート絶縁膜102を形成し、ゲート絶縁膜102上にシリコンおよびゲルマニウムを含まない第一の金属膜103を形成し、pMIS形成領域のゲート絶縁膜上に第一の金属膜103を残して、nMIS形成領域の第一の金属膜103を除去する。次に、nMIS形成領域のゲート絶縁膜102および第一の金属膜103上にシリコンまたはゲルマニウムを含む第二の金属膜104を形成し、第一および第二の金属膜103、104を加工してゲート電極Gn、Gpをそれぞれ形成する。また、第一の金属膜103と第二の金属膜104に含まれる主の金属元素は周期律表における同族金属元素とする。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、たとえメタル膜を加工したとしても、当該メタル膜の下に形成されている絶縁膜の膜減りを抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 本発明に係わる半導体装置の製造方法では、ゲート絶縁膜3上に、ゲート電極を構成するメタル膜4を形成する。その後、当該メタル膜4を加工する際に、所定の薬液を用いたウエットエッチング処理により、当該メタル膜4の一部を除去する。

(もっと読む)

トランジスタ、およびその製造方法

【課題】CMOSデバイス設計に適した仕事関数をもつメタルゲート電極を提供する。

【解決手段】

トランジスタおよびその製造工程が開示されている。相補型金属酸化膜半導体(CMOS)デバイスは、第1の厚さを有する第1ゲート電極を含むPMOSトランジスタと、第2の厚さを有する第2ゲート電極を含むNMOSトランジスタとを含み、第1の厚さは、第2の厚さよりも大きい。第1ゲート電極および第2ゲート電極は、同じ材料を含んでいることが好ましく、例として、TiSiN、TaNまたはTiNを含んでいるとよい。第1ゲート電極および第2ゲート電極の厚さによって、PMOSトランジスタおよびNMOSトランジスタの仕事関数が設定される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高品質の極薄酸化膜を均一な膜厚で再現性良く形成する。

【解決手段】半導体ウエハ1Aを酸化膜形成室107の熱処理チャンバ120へ導入する工程と、熱処理チャンバ120内のガス雰囲気を窒素によって置換する工程と、第1の温度で、触媒を用いて酸素と水素から水分を合成する工程と、合成した水分を前記酸化炉107の熱処理チャンバ120へ導入して、気化状態を維持したまま、熱処理チャンバ120内の半導体ウエハ1Aの第1主面上に水分を含んだ酸化性雰囲気を形成する工程と、熱処理チャンバ120内の水分を含んだ酸化性雰囲気において、前記第1の温度より高い第2の温度まで半導体ウエハ1Aの主面をランプ加熱して、半導体ウエハ1Aの第1主面上のシリコン表面を熱酸化処理して絶縁膜を形成する工程と、前記工程の後、熱処理チャンバ120内の前記水分を含んだ酸化性雰囲気を窒素によって置換する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性のばらつきが抑えられた半導体装置の製造方法を提供する。

【解決手段】P型MOSFETとN型MOSFETを有する半導体装置の製造方法であって、半導体基板上にゲート絶縁膜、ノンドープポリシリコン膜、金属シリサイド膜、金属ナイトライド膜、金属膜を形成する工程と、金属シリサイド膜の、P型MOSFETのゲート電極を構成する部分とN型MOSFETのゲート電極を構成する部分とが互いに分離するように、金属膜、金属ナイトライド膜および金属シリサイド膜を少なくとも加工してゲート形状にパターニングする工程と、P型およびN型のMOSFET形成領域内のノンドープポリシリコン膜にそれぞれP型およびN型不純物を導入する工程と、不純物を拡散させるための熱処理を行う工程と、不純物導入後のポリシリコン膜をゲート形状にパターニングする工程を有する半導体装置の製造方法。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高品質の極薄酸化膜を均一な膜厚で再現性良く形成する。

【解決手段】半導体ウエハ1Aを酸化膜形成室107の熱処理チャンバ120へ導入する工程と、熱処理チャンバ120内のガス雰囲気を窒素によって置換する工程と、第1の温度で、触媒を用いて酸素と水素から水分を合成する工程と、合成した水分を前記酸化炉107の熱処理チャンバ120へ導入して、気化状態を維持したまま、熱処理チャンバ120内の半導体ウエハ1Aの第1主面上に水分を含んだ酸化性雰囲気を形成する工程と、熱処理チャンバ120内の水分を含んだ酸化性雰囲気において、前記第1の温度より高い第2の温度まで半導体ウエハ1Aの主面をランプ加熱して、半導体ウエハ1Aの第1主面上のシリコン表面を熱酸化処理して絶縁膜を形成する工程と、前記工程の後、熱処理チャンバ120内の前記水分を含んだ酸化性雰囲気を窒素によって置換する工程とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子分離溝の形状を最適化してMISFETの微細化を推進する。

【解決手段】素子分離溝2に囲まれた活性領域Lの基板1の表面は、活性領域Lの中央部では平坦な水平面となっているが、活性領域Lの肩部では、素子分離溝2の側壁に向かって下降する傾斜面となっている。この傾斜面は、傾斜角度の異なる2つの傾斜面(S1、S2)を含んでいる。活性領域Lの中央部に近い第1の傾斜面(S1)は、比較的急峻な傾斜面であり、素子分離溝2の側壁に近い第2の傾斜面(S2)は、第1の傾斜面(S1)よりも緩やかな傾斜面である。また、上記活性領域Lの肩部における基板1の表面は、全体的に丸みが付けられており、角張った領域が存在しない。

(もっと読む)

半導体装置

【課題】High-k絶縁膜をゲート絶縁膜として使用する電界効果トランジスタを含む半導体装置であって、メタルゲート電極化を行わずに、フェルミレベルピニングに起因するしきい値電圧固定を抑制可能な半導体装置を実現する。

【解決手段】Pチャネル型電界効果トランジスタ4において、High-k絶縁膜たる金属酸化物(好ましくは、ハフニウム酸化物(HfO2やHfSiON、HfSiO4など)またはジルコニウム酸化物(ZrO2やZrSiON、ZrSiO4など))を有するゲート絶縁膜6bと、ポリシリコンゲート電極7との間に窒化チタン(TiN)膜8を形成する。窒化チタン膜は、金属酸化物を有するゲート絶縁膜に接して形成されてもフェルミレベルピニングが起きない。また、ポリシリコンゲート電極の下部が窒化チタン膜との金属膜となっているので、ゲートの空乏化が抑止でき、電流駆動能力向上も図れる。

(もっと読む)

半導体装置の製造方法およびシリコン窒化膜またはシリコン酸化膜の表面処理方法

【課題】ハードマスク用として形成されたシリコン窒化膜またはシリコン酸化膜を選択的にエッチングした際の残渣を、下地にダメージを与えず、かつ残存しているハードマスクを大きくエッチングすることなく除去することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板にエッチング対象膜を形成する工程と、エッチング対象膜の上にシリコン窒化膜またはシリコン酸化膜を形成する工程と、シリコン窒化膜またはシリコン酸化膜の表面に窒素を導入する工程と、シリコン窒化膜またはシリコン酸化膜を選択的にエッチング除去してエッチングマスクとする工程と、シリコン酸化膜またはシリコン酸化膜のエッチング残渣をウェットエッチングにより除去する工程と、エッチングマスクを介してエッチング対象膜をウェットエッチングする工程と、エッチングマスクを除去する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜とシリサイドゲート電極の組み合わせ技術におけるしきい値制御の問題を解決し、高性能で信頼性に優れた半導体装置を提供する。

【解決手段】シリコン基板上に、ゲート絶縁膜とこのゲート絶縁膜上に設けられたゲート電極とを有する電界効果トランジスタを備えた半導体装置において、高誘電率絶縁膜(例えばHfSiON膜)を含むゲート絶縁膜を用い、高誘電率絶縁膜に接するように下層側に設けられた、第1の金属M1(例えばNi)、M1と異なる仕事関数をもつ第2の金属M2(例えばW)およびシリコン(Si)を含むシリサイドからなる第1の層領域と、第1の層領域に接する上層側に設けられたM1(例えばNi)およびSiを含むシリサイドからなる第2の層領域とを有するゲート電極を用いる。

(もっと読む)

半導体装置

【課題】 ゲート電極の実効仕事関数をトランジスタの動作閾値電圧が最適なものとなるように制御するこを可能にする。

【解決手段】 半導体基板2と、半導体基板上に設けられたゲート絶縁膜4と、ゲート絶縁膜上に設けられたゲート電極8と、ゲート電極の両側の半導体基板に設けられたソース・ドレイン領域12、14と、ゲート電極とゲート絶縁膜との界面に、ゲート電極およびゲート絶縁膜を構成する元素と異なる電気陰性度を有する元素を含む層5と、を備えている。

(もっと読む)

多層ゲート電極及びその製造方法、ならびに多層ゲート電極が形成された半導体素子及びその製造方法

【課題】高温で安定であり、抵抗等の特性が改善され、信頼性が高い多層ゲート電極及びこれを備える半導体素子、ならびに多層ゲート電極の製造方法及び半導体素子の製造方法を提供する。

【解決手段】多層ゲート電極は、ゲート絶縁膜上に形成され導電型不純物がドープされた多結晶半導体膜と、前記多結晶半導体膜上に形成されタングステン(W1−x)及び非タングステン金属(Mx、x=0.01〜0.55)を含むオーミックコンタクト膜と、前記オーミックコンタクト膜の上に形成された金属バリヤ膜と、前記金属バリヤ膜の上に形成された高融点金属膜と、を備える。

(もっと読む)

381 - 400 / 480

[ Back to top ]