Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

441 - 460 / 480

MOS型半導体装置の製造方法およびMOS型半導体装置

【課題】 微細化された構造において仕事関数の異なるゲート電極を同一半導体基板上に形成したMOS型半導体装置を提供する。

【解決手段】 MOS型半導体装置の製造方法が、半導体基板に、第1および第2半導体素子形成領域を規定する工程と、半導体基板上に、ゲート絶縁膜、モリブデン膜、および窒素含有膜を順次積層する工程と、窒素含有膜からモリブデン膜に窒素を導入する工程と、窒素含有膜を選択的に除去し、第1半導体素子形成領域上に窒素含有膜を残す工程と、半導体基板上に、多結晶シリコン膜を形成する工程と、エッチングにより第1ゲート電極、第2ゲート電極を形成する工程と、第1および第2ゲート電極の側壁にサイドウォールを形成する工程と、熱処理により第2ゲート電極に含まれるモリブデン膜中の窒素を減少させて、第1ゲート電極に含まれるモリブデン膜中の窒素量との間に差異を設ける工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 しきい値が低い高性能の半導体装置およびその製造方法を提供する。

【解決手段】 シリコン基板10の表面部に形成されるCMOSを備える半導体装置1において、PMOS1のゲート電極G4は、窒化タングステンによる表面処理を行なったタングステン上に多結晶シリコン21を堆積させることにより形成する一方、NMOS1のゲート電極G2は、タングステン薄膜上にと多結晶シリコン21を形成した後の熱処理でタングステン薄膜をタングステンシリサイド23に反応させることにより、ゲート電極G2の仕事関数をゲート電極G4の仕事関数からシフトさせる。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】 素子量産能力を向上させることができ、E/Wサイクリング(Erase/Write cycling)及びベーク工程の際にしきい値電圧の過度なシフトを防止することができて素子の信頼性を向上させることが可能なフラッシュメモリ素子の製造方法を提供する。

【解決手段】 フラッシュメモリ素子の製造方法は、半導体基板上に酸化膜を形成する段階と、N2ガス雰囲気でプレアニーリング工程を行う段階と、流量5〜15slmのN2O雰囲気で10〜60分間メインアニーリング工程を行って前記酸化膜を窒化させ、窒化酸化膜を形成する段階と、N2ガス雰囲気でポストアニーリング工程を行う段階とを含む。

(もっと読む)

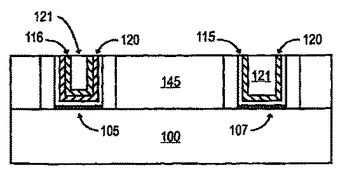

CMOS技術における自己整合デュアル・サリサイド形成のための方法

【課題】 従来のデュアル・サリサイド処理における典型的な位置ずれの問題を克服する、新規なデュアル・サリサイド・プロセスを提供すること。

【解決手段】 相補型金属酸化膜半導体(CMOS)デバイスを製作する方法であって、本方法は、第1のタイプの半導体デバイス(130)を収容するために半導体基板(102)の中に第1のウェル領域(103)を形成するステップと、第2の半導体デバイス(140)を収容するために半導体基板(102)の中に第2のウェル領域(104)を形成するステップと、第1のタイプの半導体デバイス(130)をマスク(114)で遮蔽するステップと、第2のタイプの半導体デバイス(140)の上に第1の金属層(118)を堆積させるステップと、第2のタイプの半導体デバイス(140)の上で第1のサリサイド形成を行うステップと、マスク(114)を除去するステップと、第1及び第2のタイプの半導体デバイス(130、140)の上に第2の金属層(123)を堆積させるステップと、第1のタイプの半導体(130)の上で第2のサリサイド形成を行うステップとを含む。本方法は、1つのパターン形成段階しか必要とせず、また、異なるデバイスの上に異なるシリサイド材料を形成するプロセスを単純化するため、パターンの重なりを排除することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高いフルシリサイドMOSFETおよびシリサイドMOSFETを従来よりも簡単に同一基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に第1のゲート電極40および第2のゲート電極42を形成し、第1のゲート電極および第2のゲート電極上にマスク材料90を堆積し、第2のゲート電極を被覆したまま第1のゲート電極の上面を露出させるようにマスク材料をパターニングし、マスク材料を利用して第1のゲート電極の上部をエッチングし、マスク材料を除去し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の上部をシリサイド化することを具備する。

(もっと読む)

スケーラブル集積論理および不揮発性メモリ

スケーラブル論理トランジスタはドレインおよびソースのための一組のドープされた領域を有する。ゲート絶縁層は基板上でドレイン領域とソース領域の間に形成される。ゲートスタックは、ポリシリコンや金属のようなゲート層を、二つの窒化金属層の間に置くことで形成される。また、埋め込まれた金属ナノドット層を有する高K誘電率膜を、トンネル絶縁層とゲートスタックとの間に設けるようにして付加することによって、この基本的構成から互換性のある不揮発性メモリトランジスタを形成することもできる。 (もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィー工程を削減するとともに、短チャネル効果によるサブスレッショルド電流を抑制する。

【解決手段】 フィールド形成用のシリコン窒化膜102を用いて素子分離領域105を形成した後、このシリコン窒化膜102及び半導体基板100をパターニングすることにより、半導体基板100に達するゲートトレンチを活性領域106に形成する。次に、ゲートトレンチ内にゲート電極114を形成した後、シリコン窒化膜102を除去し、これにより形成されたコンタクトホール内にコンタクトプラグを埋め込む。これにより、拡散層コンタクトパターンが不必要となるとともに、活性領域を縮小することが可能となる。しかも、ゲート電極114がゲートトレンチ内に埋め込まれていることから、ゲート長が拡大され、サブスレッショルド電流を抑制することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、ゲート電極の空乏化を抑制すると共に、シリサイドの高抵抗化を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜上に、所定の半導体材料とゲルマニウムとを含む膜を形成するステップと、膜を酸化することにより、ゲート絶縁膜上に、当該膜よりもゲルマニウム濃度が高くかつ膜厚が薄い第1の膜を形成すると共に、第1の膜上に酸化膜を形成するステップと、酸化膜を除去するステップと、第1の膜上に、半導体材料を含み、第1の膜よりもゲルマニウム濃度が低い第2の膜を形成するステップと、第2の膜及び第1の膜にエッチングを行うことにより、ゲート電極を形成するステップとを備えることを特徴とする。

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

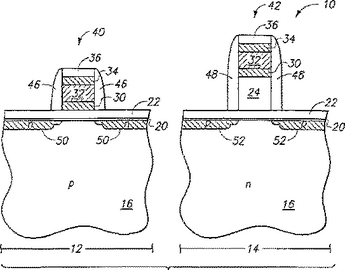

CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法

【課題】CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法を提供する。

【解決手段】本発明の一実施形態によると、半導体装置を形成する方法は、半導体本体(14)の外面上にゲートスタック(22)を形成する段階を含む。第1及び第2の側壁本体(34)が、ゲートスタックの対向する側に形成される。ゲートスタックのゲート導電体(24)の外面に第1の凹部(36a)が形成され、この第1の凹部が形成された後にゲートスタックの中に第1のドーパント(40)が注入される。第1のドーパントは、第1の凹部を形成するゲートスタックの外面から内向きに拡散する。第1のドーパントは、ゲートスタックと半導体本体の間のインタフェースに向って拡散する。第1の凹部は、インタフェースにおいて第1のドーパントの濃度を増加させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が微細化しても細線効果による性能低下を抑制できる、高集積化に適した新たな3次元半導体装置及びその製造方法を提供することである。

【解決手段】 上記課題を解決した半導体装置は、半導体層中にこの半導体層表面に垂直に形成されたトレンチと、前記トレンチの側面及び底面の前記半導体層中に形成され、前記トレンチの深さ方向に形成された複数の素子分離と、前記トレンチの側面に沿って形成され、絶縁膜と電極とを備えた複数の機能素子と、前記電極に接続し、前記複数の機能素子を第1の方向に接続する第1の配線と、前記トレンチの側面及び底面の前記半導体層中に形成され、前記素子分離により分離され、前記機能素子を前記第1の方向は異なる第2の方向に電気的に接続する第2の配線とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】フォトレジスト膜の除去の際の洗浄における半導体層上のシミのない半導体装置の製造方法を提供する。

【解決手段】露出している半導体層の表面部を酸化して、アッシング酸化膜17を形成した後、CVD酸化膜を堆積する。CVD酸化膜の上に形成したフォトレジスト膜9をマスクとする気相フッ酸処理により、アッシング酸化膜17は残したままでCVD酸化膜を部分的に除去し、非シリサイド領域Rnsを覆う反応防止用酸化膜18を形成する。フォトレジスト膜9を除去した後、アッシング酸化膜17を除去し、乾燥処理を行なった後、基板上に金属膜を堆積する。そして、半導体層と金属膜との反応により、高濃度ソース・ドレイン領域11などの半導体層の上部にシリサイド層12を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上に形成されるトランジスタの導電型によらず、移動度を向上させる。

【解決手段】 半導体装置は、シリコン基板1上にPMOSトランジスタ2と、NMOSトランジスタ3とを備えている。いずれのトランジスタも、シリコン基板1上に形成されるゲート絶縁膜4と、このゲート絶縁膜4上に形成されるゲート電極5a,5bとを有する。ゲート電極5a,5bは例えばタングステン(W)で形成されている。PMOSトランジスタ2のゲート電極5aとNMOSトランジスタ3のゲート電極5bとに、互いに異なる応力を持たせる。

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィー工程を削減するとともに、活性領域の縮小により半導体装置の集積度を高める。

【解決手段】 フィールド形成用のシリコン窒化膜102を用いて素子分離領域105を形成した後、このシリコン窒化膜102をパターニングすることによりゲートトレンチ114bを形成する。次に、ゲートトレンチ114b内にゲート電極材料111〜113を埋め込み、これをエッチバックした後、シリコン窒化膜102を除去する。そして、これにより形成されたコンタクトホール内にコンタクトプラグを埋め込む。これにより、拡散層コンタクトパターンを用いることなく、コンタクトプラグを形成できるとともに、コンタクトプラグの周縁が素子分離領域と活性領域の境界と実質的に一致することから、活性領域を縮小することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】 容量素子及びヒューズ素子を有し、フォトリソグラフィ工程を追加することなく製造可能な半導体装置を提供する。

【解決手段】 半導体基板の表面に形成された絶縁膜(5)の一部の領域上に容量素子(10)及びヒューズ素子(20)が配置されている。容量素子は、下部電極、容量誘電体膜、シリコンからなる第1の上部電極、及び該第1の上部電極よりも抵抗率の低い材料からなる第2の上部電極が構成される。ヒューズ素子は、下層、中層、及び上層が積層された積層構造を有する。ヒューズ素子の下層と容量素子の下部電極、中層と第1の上部電極、上層と第2の上部電極が、それぞれ同一の材料で形成され、かつ同一の厚さを有する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極上に形成するコンタクトホールの底面の金属膜の表面が酸化されるのを抑制する。

【解決手段】 基板上コンタクトホール19a、19bと、底面に金属膜7aを露出させたゲート電極上コンタクトホール19cとを形成した後、基板上コンタクトホール19a、19bの底面に露出したシリコン基板1にそれぞれ不純物を注入してN型イオン注入層21、P型イオン注入層23を形成する。その後、基板上コンタクトホール19a、19bおよびゲート電極上コンタクトホール19cが埋め込まれない膜厚で、これらのコンタクトホールの内面に金属酸化防止膜24を形成する。そして、熱処理により不純物を活性化させた後に、それぞれのコンタクトホールの底面の金属酸化防止膜24を除去する。

このように形成することにより、上記熱処理において金属膜7aの表面が酸化されるのを抑制することができる。

(もっと読む)

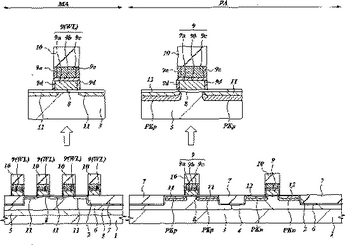

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルトランジスタと低電圧トランジスタと高電圧トランジスタのゲート電極の間に絶縁膜を埋め込むことが容易な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルトランジスタのトンネル絶縁膜15と低電圧トランジスタの低電圧ゲート絶縁膜14と高電圧トランジスタの高電圧ゲート絶縁膜16を半導体基板7の上に形成する。第1のn型半導体膜17をトンネル絶縁膜15と低電圧ゲート絶縁膜14と高電圧ゲート絶縁膜16の上に成膜する。第1絶縁膜19を第1のn型半導体膜17の上に成膜する。第2のn型半導体膜21を露出した第1の半導体膜17と第1絶縁膜19の上に形成する。メモリセルトランジスタの制御ゲート電極23と低電圧トランジスタと高電圧トランジスタのゲート電極21、23をマスクに第2のn型半導体膜21においてn型不純物の濃度よりp型不純物の濃度が低くなるようにp型不純物のイオン注入を行い半導体基板7内に導電型がp型であるソース・ドレイン領域38を形成する。

(もっと読む)

441 - 460 / 480

[ Back to top ]