Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

81 - 100 / 743

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

半導体装置

【課題】MISFETにおけるAvt(Vtばらつき)のゲート幅依存性を考慮し、Vtミスマッチ及びVtばらつきを低減できるようにする。

【解決手段】半導体装置は、それぞれが半導体基板に形成され、ソースドレインを構成する拡散層205及び該拡散層205の上に形成されたゲート203を有し、且つ互いに並列接続された複数の単位MISFETから構成される複数のMISFET201、202を含む。MISFET201、202同士の間の閾値電圧のばらつきの標準偏差は、各MISFETにおける単位MISFETのそれぞれのゲート長とゲート幅との積の総和であるチャネル面積と同一の面積を有する単一のMISFET同士の間の閾値電圧のばらつきの標準偏差よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETにSiGe層が成長されることを抑制し、かつPMOSFETのSiGe層の形状不良の発生を抑止する。

【解決手段】半導体装置の製造方法は、半導体基板の第1領域に第1ゲート電極6Aを形成し、前記半導体基板の第2領域に第2ゲート電極6Bを形成し、前記第1ゲート電極の側壁に第1サイドウォール12Aを形成し、前記第2ゲート電極の側壁に第2サイドウォール12Bを形成し、前記半導体基板、前記第1ゲート電極、前記第2ゲート電極、前記第1サイドウォール及び前記第2サイドウォールを覆うように酸化膜20を形成し、前記酸化膜上に、前記第1領域を覆うようにレジストを形成し、前記レジストをマスクとして前記酸化膜20をエッチングすることにより、前記第2領域の前記酸化膜20を除去し、前記レジストを除去し、前記半導体基板及び前記第1領域の前記酸化膜20に対して、塩素を含むガスを用いてプラズマ処理を行う。

(もっと読む)

SeOI上の疑似インバータ回路

【課題】メモリアレイのワードライン・ドライバ回路として使用できる、大きくなく、低消費電力の回路を提供する。

【解決手段】半導体・オン・インシュレータ(SeOI)基板上に形成された回路であって、電源電位を印加する為の第1、第2の端子間に第2のチャネル型のトランジスタと直列の第1のチャネル型のトランジスタを含み、トランジスタの各々が薄層におけるドレイン領域およびソース領域と、ソース領域とドレイン領域間に延びるチャネルと、チャネルの上方に配置されたフロント・コントロール・ゲートとを備え、各トランジスタが、トランジスタのチャネルの下方のベース基板に形成され、かつトランジスタの閾値電圧を調整する為にバイアスされうるバック・コントロール・ゲートを有し、トランジスタのうちの少なくとも1つが閾値電圧を十分に調整するバックゲート信号の作用の下、空乏モードで動作するように構成される。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】閾値電圧の制御性を向上させて形成された複数種類のトランジスタを備える不揮発性記憶装置、および、それに適した製造方法を提供する。

【解決手段】1つの半導体基板2の表面に形成された複数種類のMOSトランジスタを有する不揮発性記憶装置であって、n形のソース領域14およびドレイン領域15と、その間の半導体基板2の表面上に設けられたゲート絶縁膜17と、ゲート電極18と、ゲート絶縁膜17の直下に位置し、n形不純物とp形不純物との両方を含むチャネル領域42と、を有するMOSトランジスタ10と、n形のソース領域24およびドレイン領域25と、その間の半導体基板2の表面上に設けられたゲート絶縁膜27と、ゲート電極28と、ゲート絶縁膜27の直下に位置し、n形不純物の濃度プロファイルがチャネル領域42と同じであるチャネル領域43と、を有するMOSトランジスタ20と、を備える。

(もっと読む)

フィン型電界効果トランジスタおよびその製造方法

【課題】フィン型電界効果トランジスタおよびその製造方法を提供する。

【解決手段】半導体基板より上に延伸したfinFETの第1および第2のフィン206を、その間にシャロートレンチアイソレーション(STI)領域202、およびSTI領域の上面と第1および第2のフィンの上面との間の距離を有して、形成するステップ、STI領域の上面より上の第1および第2のフィンの上面および側面に第1および第2のフィン延伸部を提供するステップ、STI領域から材料を除去し、STI領域の上面と第1および第2のフィンの上面との間の距離を増加させるステップ、フィンおよびSTI領域上に共形のストレッサ誘電材料214を堆積するステップ、および共形のストレッサ誘電材料をSTI領域の上面より上の第1および第2のフィンの間の空間内に流入するようにリフローし、finFETのチャネルに応力を加えるステップを含む方法。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置及びその製造方法

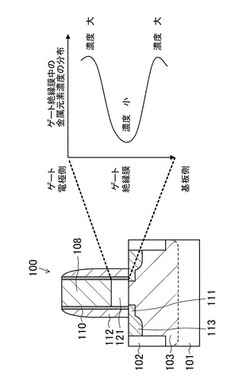

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタ

【課題】伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタを提供する。

【解決手段】本発明は、単一端子トランジスタ装置に関する。一具体例において、nチャネルトランジスタは、離散正孔準位H0を有する第一半導体層と、伝導帯底EC2を有する第二半導体層と、第一半導体層と第二半導体層の間に配置される広バンドギャップ半導体バリア層と、第一半導体層の上方のゲート誘電層と、ゲート誘電層の上方にあり、ゼロバイアスを加え、n端子特徴を得るために、離散正孔準位H0が伝導帯底Ec2の下方に位置するように選択された有効仕事関数を有するゲート金属層と、からなる。

(もっと読む)

絶縁膜下の埋め込みバック・コントロール・ゲートを有するSeOI上の同型のトランジスタからなる回路

【課題】リソグラフィーパターン転写に存在する変動性によって発生する問題の解決、STIを使用せず、構造を厳密化して空間を節約すること、転写されるべきより規則的かつ緻密な構造の提供。

【解決手段】SeOI基板上に形成された半導体デバイスであり、電界効果トランジスタから形成された行の形で配置されパターンのアレイを備え、電界効果トランジスタのチャンネル領域の上方に形成されたフロント・コントロール・ゲート領域を備え、各行に含まれるソース領域およびドレイン領域も同じ寸法を有し、かつ所定の寸法を有するフロント・コントロール・ゲート領域だけ隔てられ、パターンに含まれる少なくとも1つのトランジスタT1〜T4がチャンネル領域の下方に存在するベース基板内に形成されたバック・コントロール・ゲート領域を有し、トランジスタのしきい電圧をシフトさせて、バック・コントロール・ゲート領域がバイアスされることを可能とする。

(もっと読む)

トランスミッションゲート及び半導体装置

【課題】様々な入力電圧に対応して高S/N特性を実現できるトランスミッションゲートを提供する。

【解決手段】入力電圧Vinをドレインから入力され、電圧(Vin−Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するPMOSトランジスタ11と、PMOSトランジスタ11と等しいゲート長とゲート幅とゲート酸化膜厚と閾値電圧の絶対値とを有し、入力電圧Vinをドレインから入力され、電圧(Vin+Vs1)をゲートに入力されるとオンし、入力電圧Vinを出力電圧Voutとしてソースから出力するNMOSトランジスタ12と、を備える。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

81 - 100 / 743

[ Back to top ]