Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

161 - 180 / 743

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチの側壁部の上部における寄生トランジスタのしきい値電圧の低下を抑制する。

【解決手段】半導体装置は、半導体基板100におけるFET形成領域に形成されたMISトランジスタを備えている。半導体基板100に設けられたトレンチ104内に形成され、FET形成領域を区画するシリコン酸化膜107と、FET形成領域及びシリコン酸化膜107の上に形成されたゲート絶縁膜110と、ゲート絶縁膜110の上に形成されたゲート電極111とを備えている。ゲート絶縁膜110のうち、トレンチ104内に位置するゲート電極111と半導体基板100の側面との間に形成されている部分は、アルミニウムを含有している一方、ゲート絶縁膜110のうち、ゲート電極111と半導体基板100の上面との間に形成されている部分は、アルミニウムを含有していない。

(もっと読む)

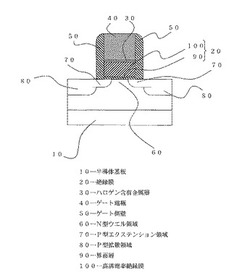

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体装置の製造方法

【課題】nMOSFETのソース/ドレイン領域にはSiGeを埋め込まず、pMOSFETのソース/ドレイン領域にのみSiGeを再現性よく埋め込むことが可能な製造方法を提供する。

【解決手段】第1活性領域12と交差する第1ゲート電極21、及び第2活性領域13と交差する第2ゲート電極22を形成し、第1及び第2ゲート電極を覆うように、第1キャップ膜35を形成する。第1活性領域上の第1キャップ膜35を、エッチングして除去する。半導体基板全面に、第2キャップ膜を形成37する。第2活性領域上の第2キャップ膜37を第2マスクパターンで覆い、第1活性領域上の第2キャップ膜37をエッチングして除去する。第2活性領域を第1及び第2キャップ膜で覆った状態で、第1活性領域において、ソース/ドレイン領域をエッチングすることにより、凹部を形成する。凹部内を、埋込部材で埋め込む。

(もっと読む)

半導体装置

【課題】回路動作の安定性を高め、消費電力の低減を可能とした半導体装置を提供する。

【解決手段】フローティングボディ型のPD−SOI−MOSFET21〜26を有する分周回路を備え、この分周回路の動作時は、MOSFET22、23,24、26の各ゲート(G)に固定電圧が印加されてMOSFET22、24がオンすると共に、MOSFET23、26がオフする。また、MOSFET21、25の各ゲート(G)に振幅電圧が印加されて、MOSFET21、25がオン、オフを繰り返す。このように動作する分周回路において、MOSFET23、26の閾値電圧の絶対値は、例えばチャネルドープにより、MOSFET21、25の閾値電圧の絶対値よりも大きく設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】偏析不純物による仕事関数の制御の可能な半導体装置または半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に設けられた絶縁膜(HfSiON膜30)と、絶縁膜30上にフルシリサイド電極(NiSi51)と、フルシリサイド電極51に接するように、絶縁膜30とフルシリサイド電極51の間に設けられたバリア膜(SiOC膜40)と、を備え、SiOC膜40と接するフルシリサイド電極51の部分に、N型またはP型いずれかの不純物60が偏析し、SiOC膜40は、シリコン酸窒化膜の誘電率以下の誘電率を有し、以下の(a)、(b)および(c)を主成分として含み、((a)シリコン(Si)、(b)炭素(C)、(c)酸素(O)または窒素(N))、HfSiON膜30またはNiSiフルシリサイド電極51を構成する金属元素を主成分としてバリア膜の少なくとも内部に含まないもの。

(もっと読む)

基準電圧発生回路装置の製造方法

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の厚さが異なるトランジスタを有する半導体装置の製造歩留まりを向上させる。

【解決手段】シリコン基板1上に高耐圧絶縁膜IH1を形成した後、高耐圧絶縁膜IH1の表面を削って膜厚を薄くし、高耐圧絶縁膜IH1と隣接するようにして中耐圧絶縁膜IM1を形成する。高耐圧絶縁膜IH1は、熱酸化法によって、シリコン基板1の主面より内側から外側に至るようにして形成し、中耐圧絶縁膜IM1は高耐圧絶縁膜IH1より薄くなるようにして形成する。高耐圧絶縁膜IH1は高耐圧MISトランジスタのゲート絶縁膜として、中耐圧絶縁膜IM1は中耐圧MISトランジスタのゲート絶縁膜として形成する。

(もっと読む)

半導体装置

【課題】論理回路に向けた製造プロセスで製造できるパワーMOSFET及び論理回路を有する半導体装置を提供する

【解決手段】半導体装置は、パワーMOSと論理回路とを有する。第1領域が第1方向及び第1方向と直交する第2方向に並んで複数個配置され、周囲にガードリング領域が設けられて第2領域が構成され、更に第2領域が第1方向及び第2方向に並んで複数個配置されて第3領域で構成される。第1領域は、第1方向に延長され、第2方向に並んで配置された複数のゲート電極及びソース,ドレインを有する複数のMOSFET及びバックゲート領域及びそれぞれを相互に接続する第1配線層を有する。第3領域において、第2方向に延長されてそれぞれ相互に接続する第1配線層同士を接続する第2配線層、第1方向に延長されて第2配線層同士を接続する第3配線層とが設けられてパワーMOSFETが形成される。

(もっと読む)

スレッショルド調節半導体合金を堆積させるのに先立ちパターニング不均一性を低減することによる前記半導体合金の厚みばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体合金を堆積させるための選択的エピタキシャル成長プロセスにおける成長速度は、選択的エピタキシャル成長プロセスを実行するのに先立ちプラズマ支援エッチングプロセスを実行することによって、高められ得る。例えば、プラズマ支援エッチンプロセスに基いてマスク層がパターニングされてよく、それにより後続の成長プロセスの間に優れたデバイストポグラフィを同時にもたらすことができる。従って、スレッショルド調節材質を高い厚み均一性で堆積させることができ、全体的なスレッショルドばらつきを低減することができる。

(もっと読む)

半導体装置

【課題】複数種類の閾値電圧のMISトランジスタをフォトレジスト数及び不純物拡散工程を追加することなく、閾値電圧を高くしてもリーク電流を低減することが可能な半導体装置を提供すること。

【解決手段】半導体基板1のチャネル領域1a、1b上にゲート絶縁膜4a、4bを介してゲート電極5a、5bが形成されるとともにチャネル領域1a、1bの両側にソース/ドレイン領域8a〜8dが形成された複数のMISトランジスタHVT、MVTを備え、ゲート電極5a、5bは、プラグ10a、10bを介して配線11a、11bに電気的に接続され、配線11a、11b上に、複数のビア13a、13bが形成され、複数のMISトランジスタHVT、MVTは、対応するゲート絶縁膜4a、4bにトラップされる電荷量が異なることにより、互いに閾値電圧が異なる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置の製造方法

【課題】面方位が(110)面あるいはこれと等価な面であるシリコン層上に形成する酸化膜厚の制御を行うことのできる半導体装置の製造方法を提供すること。

【解決手段】面方位が(110)面あるいはこれと等価な面であるシリコン基板1表面の一部に、リンのイオン注入を行って、端部の不純物濃度が連続的に変化した第1の不純物領域2Aを形成する工程と、熱酸化を行って、シリコン基板1上に端部の厚さが連続的に変化したシリコン酸化膜3を形成する工程と、を含むこと、を特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の空乏化と、ゲート電極内の不純物量の減少ないしはバラつきと、イオンがゲート絶縁膜を突き抜けてしまうことに起因したゲート絶縁膜の信頼性低下及び閾値変動を抑制する。

【解決手段】第1注入工程(図1(b)、図1(c))と第2注入工程(図1(d)、図1(e))を備える。第1注入工程ではゲート絶縁膜5と、ゲート電極9、10となる膜6と、が形成された半導体基板1のゲート電極9、10となる部分に、n型又はp型の導電型のイオンを注入する。第2注入工程では、ゲート電極9、10に同じ導電型のイオンを注入する。第1注入工程で注入するイオンの質量は、第2注入工程で注入するイオンよりも大きくする。これにより第1注入工程による不純物の濃度分布の縦方向におけるピーク位置を、第2注入工程による不純物のピーク位置よりもゲート絶縁膜5寄りにする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート絶縁膜とゲート電極の間の領域に導入するハフニウムを、pMOSFE

TとnMOSFETで、適した面密度とすることで、CMOSFETの性能向上を図る。

【解決手段】

シリコン基板2上にpMOSFET10とnMOSFET30を備えるCMOSFET

1において、pMOSFET10は、シリコン基板2上に形成されたゲート絶縁膜12と

、ゲート絶縁膜12上に形成されたハフニウム層14と、ハフニウム層14上に形成され

たゲート電極13とを備える。nMOSFET30は、シリコン基板2上に形成されたゲ

ート絶縁膜32と、ゲート絶縁膜32上に形成されたハフニウム層34と、ハフニウム層

34上に形成されたゲート電極33とを備える。ハフニウム層34の面密度は、ハフニウ

ム層14の面密度より低い。

(もっと読む)

半導体装置及びその製造方法

【課題】high-k膜とメタルゲート電極とを有する同一導電型の2つ以上のトランジスタが同一基板内に形成された半導体装置において、閾値電圧の差をチャネル領域における不純物濃度の差に由来する閾値電圧の差よりも大きくすることは難しかった。

【解決手段】半導体装置は、第1のトランジスタと、第1のトランジスタと同一導電型の第2のトランジスタとを備えている。第1のトランジスタは、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜8aと、第1のゲート電極11aとを備えている。第2のトランジスタは、高誘電体材料と第1の金属と閾値電圧調整用不純物とを含有する第2のゲート絶縁膜8bと、第2のゲート電極11bとを備えている。第1のゲート絶縁膜8aは、第2のゲート絶縁膜8bに比べて閾値電圧調整用不純物の濃度が低い、又は閾値電圧調整用不純物を含有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧の絶対値が互いに異なる複数のMISトランジスタが用いられる場合において、しきい値電圧の絶対値が大きい方のMISトランジスタの駆動電流の低下を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】第2のnMISトランジスタT2nのしきい値電圧は、第1のnMISトランジスタT1nのしきい値電圧よりも大きく、第2のnMISトランジスタT2nが有する第2のnMIS高誘電率膜H2nにおけるランタン原子濃度およびマグネシウム原子濃度の和は、第1のnMISトランジスタT1nが有する第1のnMIS高誘電率膜H1nにおけるランタン原子濃度およびマグネシウム原子濃度の和よりも小さい。

(もっと読む)

半導体デバイスとその製造方法、および集積回路

【課題】 バンド端を制御されたVtオフセット・デバイスを提供する。

【解決手段】 バンド端を制御されたVtオフセット・デバイス、バンド端を制御されたVtオフセット・デバイスの設計構造体、及びその構造体の製造方法を開示する。構造体は、第1のバンド構造及び第1の型をもたらす第1の原子比の第1の化合物半導体のチャネルを有する第1のFETを含む。この構造体はさらに、第2のバンド構造及び第1の型をもたらす第2の原子比の第2の化合物半導体のチャネルを有する第2のFETを含む。第1の化合物半導体は第2の化合物半導体とは異なり、その結果、第1のFETは第2のバンド構造とは異なる第1のバンド構造を有し、第2のFETの閾値電圧とは異なる閾値電圧を生じる。

(もっと読む)

半導体装置及びその製造方法

【課題】拡大された底部トレンチに、確実に分離膜を充填することで、トレンチ分離の縮小効果を維持しつ、高耐圧の分離膜を形成する技術を提供することを課題とする。

【解決手段】基板に形成された上部トレンチと前記上部トレンチの下に形成された底部トレンチとからなるトレンチを備え、前記底部トレンチが、前記上部トレンチより広い幅を有し、かつSOG膜又は熱酸化膜で埋め込まれ、前記上部トレンチが酸化膜で埋め込まれていることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

チャネル半導体合金を備えたトランジスタにおける堆積不均一性の低減によるスレッショルド電圧ばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体材質が、高い堆積均一性に基いて1つのタイプのトランジスタに対して選択的に設けられ得る。この目的のために、半導体合金は、任意のトランジスタの能動領域上に堆積させられてよく、そして高度に可制御なパターニングレジームに基いて次いでパターニングされてよい。その結果、スレッショルドばらつきが低減され得る。

(もっと読む)

161 - 180 / 743

[ Back to top ]