Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

121 - 140 / 743

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

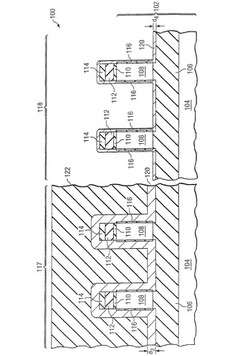

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

有機FETアレイ

【課題】pチャネルとnチャネルに共通の有機半導体層とソース、ドレイン電極材料の好適な組合せにより、実用上十分に良好な伝達特性を得ることが可能な有機FETアレイを提供する。

【解決手段】有機半導体層を用いたpチャネル電界効果トランジスタ(p型有機FET)と、有機半導体層を用いたnチャネル電界効果トランジスタ(n型有機FET)とを備えた有機FETアレイ。有機半導体層5はpチャネルとnチャネルに共通の材料の有機半導体単結晶により形成される。p型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが正孔になるように選択されたpチャネル金属電極6により形成され、n型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが電子になるように選択されたnチャネル金属電極7により形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体集積回路

【課題】回路設計の余裕を拡大すること。

【解決手段】半導体集積回路100は、トランジスタ124a,124bと、検出回路131と、バイアス生成回路132と、を備えている。トランジスタ124aおよびトランジスタ124bは、基板にバイアスが印加される。検出回路131は、トランジスタ124aおよびトランジスタ124bの閾値電圧を検出する。バイアス生成回路132は、検出回路131による検出結果に基づいてバイアスを生成する。

(もっと読む)

半導体装置

【課題】電源回路等を追加することなく、第1の電源電圧が低下してもダイナミックVTによる高速化の効果の低減を抑制できる半導体装置を提供する。

【解決手段】第1の回路は、第1の電源電圧を供給する第1の電源ラインと第1の電源電圧よりも低い第2の電源電圧を供給する第2の電源ライン間に接続された、トランジスタを備える。制御回路は、第1の電源ラインと第2の電源ライン間に接続され、上記トランジスタのバックゲートに第1の電源電圧と第2の電源電圧の電位差よりも振幅が大きい制御信号を供給する。

(もっと読む)

集積回路の信頼性を評価するための方法及びシステム

【課題】 多数の電界効果トランジスタを有する集積回路の信頼性を評価するための方法及び回路システムを提供する。

【解決手段】 本発明は、方法を提供する。この方法は、第1の動作条件下で複数の電界効果トランジスタ(FET)を動作させることと、短時間、複数のFETの少なくとも1つについての動作方向を逆にすることと、短時間、複数のFETの1つの第2の動作条件を測定することと、第2の動作条件と基準動作条件との間の差を計算することと、第2の動作条件と基準動作条件との間の差に基づいて信頼性インジケータを提供することとを含み、複数のFETは、単一の集積回路(IC)において用いられる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体集積回路

【課題】サブスレッショルドリーク電流が増大するという問題を回避しつつ、動作時における消費電力を極力低減し得る半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のFF103、組み合わせ回路104及びメインFF105と、メインFF105と並列に設けられる第1の遅延素子107及び第1のカナリアFF108と、メインFF105と並列に設けられる第2の遅延素子111及び第2のカナリアFF112と、メインFF105の出力と第1のカナリアFF108の出力とを比較する第1の比較回路109と、メインFF105の出力と第2のカナリアFF112の出力とを比較する第2の比較回路113と、第1の比較回路109の出力及び第2の比較回路113の出力に応じて、組み合わせ回路104のトランジスタの閾値電圧を制御する制御回路120とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置、半導体装置の製造方法、電子機器および電子機器の製造方法

【課題】回路特性の向上が可能な、有機トランジスタよりなる論理回路を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ドライバトランジスタ(PTD)とロードトランジスタ(PTL)を有する論理回路を含む半導体装置であって、ドライバトランジスタの能動層は、第1のp型有機半導体層(5D)からなり、ロードトランジスタの能動層は、第2のp型有機半導体層(5L)からなり、ロードトランジスタの閾値電圧(VthL)はドライバトランジスタの閾値電圧(VthD)よりも高い。p型有機半導体(5D,5L)の膜厚を変えることにより、閾値を変化させる。p型有機半導体(5D,5L)の材料を変えることにより、閾値を変化させる。第1のp型有機半導体層(5D)にドナーを含ませる。第2のp型有機半導体層(5L)にアクセプターを含ませる。かかる構成により、論理回路の特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させる。特に、nチャネル型のMOSFETにおけるVthのローカルばらつきAvtを低減させる。

【解決手段】co−impla技術を用い、nチャネル型のMOSFETのエクステンション領域9aに窒素をシリコン基板1の主面に対して垂直もしくは垂直に近い角度(0〜3度)で打ち込むことにより、窒素が打ち込まれて形成された欠陥トラップ層もしくはアモルファス層がアニ−ル後のシリコン基板1表面近傍への不純物のパイルアップを軽減するため、チャネル表面近傍のドーパントの濃度が低減し、シリコン基板1表面近傍における不純物プロファイルの揺らぎ成分が軽減される。その結果、チャネル表面近傍の不純物揺らぎ起因のローカルばらつきを抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】

CMOSトランジスタの一方のキャップ誘電体膜に対するアニール条件を、CMOSトランジスタの他方のキャップ誘電体膜に対するアニール条件とは独立に設定する。

【解決手段】

シリコン基板に、n型ウェルおよびp型ウェルを形成し、シリコン基板上方にHfO等の第1の高誘電率絶縁膜、AlO等の第1のキャップ誘電体膜を積層し、p型ウェル上方から、少なくとも第1のキャップ誘電体膜を除去し、第1の温度で第1のアニールを行なって、第1のキャップ誘電体膜の構成元素Al等をn型ウェル上方の第1の高誘電率絶縁膜中へ拡散させ、p型ウェルおよびn型ウェル上方にHfO等の第2の高誘電率絶縁膜、LaO等の第2のキャップ誘電体膜を積層し、n型ウェル上方の第2のキャップ誘電体膜を除去し、第1の温度より低い第2の温度で、第2のアニールを行なって、第2のキャップ誘電体膜の構成元素La等をp型ウェル上方の第2の高誘電率絶縁膜中へ拡散させる。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】第1の逆スタガ型薄膜トランジスタ及び第2の逆スタガ型薄膜トランジスタにより構成されるEDMOS回路を有する論理回路部を有し、第1の逆スタガ型薄膜トランジスタは、第1のゲート電極、ゲート絶縁層、第1の半導体層、第1の一対の不純物半導体層、及び第1の一対の配線を有し、第1の半導体層は、ドナーとなる不純物元素を含む微結晶半導体層と、混合領域と、非晶質半導体を含む層とが積層され、第2の逆スタガ型薄膜トランジスタは、第2のゲート電極、ゲート絶縁層、第2の半導体層、第2の一対の不純物半導体層、及び第2の一対の配線を有し、第2の半導体層は、微結晶半導体層と、非晶質半導体層とが積層されている表示装置。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】PチャネルMOSFETの閾値電圧の上昇を防ぎつつ、NチャネルMOSFETの閾値電圧の制御を確実に行う。

【解決手段】半導体装置1は、半導体基板10にゲート絶縁膜を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜に開口部を有し、かつゲート絶縁膜を覆うマスクを形成し、NチャネルMOSFET形成領域に位置するゲート絶縁膜上、およびPチャネルMOSFET形成領域に形成されたマスク上に第1の金属層を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜中に第1の金属層を形成する金属を熱処理により拡散させること、により製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

121 - 140 / 743

[ Back to top ]