Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

61 - 80 / 743

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の特性を劣化させることなく、浅い接合の半導体装置を提供する。

【解決手段】まず、半導体基板上に、ゲート絶縁膜を形成する(s100)。次いで、ゲート絶縁膜上にゲート電極を形成する(s200)。次いで、ゲート電極を形成する工程(s200)の後、第一アニール工程を行う(s300)。次いで、第一アニール工程(s300)の後、ゲート電極の両側における半導体基板に、ポケット領域およびエクステンション領域を構成する不純物注入を行う(s400)。その不純物注入を行う工程(s400)の後、第二アニール工程として、最高アニール温度が1000℃以上で、アニール時間が100ミリ秒以下であるアニールを行う(s700)。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

半導体装置

【課題】低消費電力で高速シリアル伝送が可能な半導体装置を提供する。

【解決手段】実施形態によれば、インタフェース部と、駆動回路部と、スイッチ部と、電源回路部と、を備えた半導体装置が提供される。前記インタフェース部は、フローティング状態のバックゲートを有しSOI基板上に設けられた第1のMOSFETを含み、入力したシリアルデータの端子切替信号をパラレルデータに変換する。前記電源回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第2のMOSFETを含み、前記インタフェース部に供給される電源の電位よりも高いオン電位を生成する。前記駆動回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第3のMOSFETを含み、前記パラレルデータに応じて、前記オン電位をハイレベルとする制御信号を出力する。前記スイッチ部は、前記SOI基板上に設けられ、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

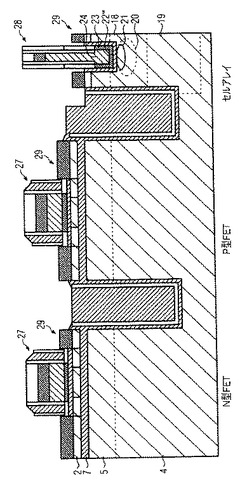

半導体装置、および半導体装置の製造方法

【課題】同一の極性を有する複数の薄膜FETの閾値電圧に差をつけて、半導体装置の性能の最適化を図ることができる。

【解決手段】半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に形成された薄膜n型FET100と、埋め込み絶縁膜2上に形成された薄膜p型FET101と、埋め込み絶縁膜2上に形成された薄膜n型FET100bと、薄膜n型FET100のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4と、薄膜p型FET101のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域5と、薄膜n型FET100bのチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4bと、を備え、p型ウェル領域4、4b、5は、n型ウェル領域40によって囲まれており、かつ互いに接触していない。

(もっと読む)

半導体装置及びサンプルホールド回路

【課題】ON状態での低いオン抵抗とOFF状態での小さいオフリーク電流を持つMOSトランジスタスイッチを用いた半導体装置及びサンプルホールド回路を実現する。

【解決手段】PMOSトランジスタM11がON状態の場合には、PMOSトランジスタM12がON状態になりPMOSトランジスタM11のバックゲート端子をPMOSトランジスタM11のソース端子に接続し、PMOSトランジスタM11がOFF状態の場合には、PMOSトランジスタM13がON状態になりPMOSトランジスタM11のバックゲート端子を電源電圧端子VDD1に接続する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入で所定の元素をゲート電極に導入して、異なる仕事関数を有するゲート電極のMOSトランジスタを形成する際に、製造工程の増加を抑制して低コストの半導体装置を提供する。

【解決手段】半導体装置の製造方法では、導電膜上5a,5bにおいて、第1の領域1aから第2の領域1bまでを覆う第1のマスク6b、第2の領域の上方にスペース部7b、及び第2の領域1bから第3の領域1cまでを覆う第2のマスク6cを有するマスクパターンを設ける。スペース部内、並びに第1及び第2のマスクの第1の側面にサイドウォール膜7aを設ける。第1の側面に接するサイドウォール膜の下に位置する導電膜の領域内に不純物を注入する。サイドウォール膜をマスクに用いて異方性エッチングを行うことによりゲート絶縁膜及びゲート電極を形成してMOSトランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に設けられた第1の薄膜FET100と、第1の薄膜FET100と隣接して埋め込み絶縁膜2上に形成された第2の薄膜FET101と、第1の薄膜FET100直下の半導体基板1内に設けられた第1ウェル領域4と、第2の薄膜FET101直下の半導体基板1内に設けられた第2ウェル領域5と、を備え、第1ウェル領域4から第2ウェル領域5までの距離が、第1の薄膜FET100から第2の薄膜FET101までの距離よりも大きい。

(もっと読む)

61 - 80 / 743

[ Back to top ]