Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

101 - 120 / 743

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

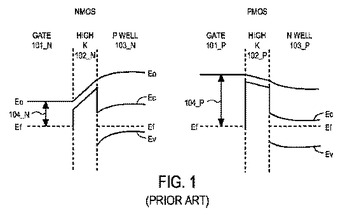

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

スイッチング装置

【課題】寄生容量が低減し、ラッチアップ耐性が向上したスイッチング装置を提供する。

【解決手段】半導体層と、前記半導体層の表面に選択的に形成され、ソース領域とドレイン領域とが表面に選択的に形成された第1のウェル領域と、前記半導体層と前記第1のウェル領域との間に形成された第2のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された、第1の入出力端子と、前記ドレイン領域に接続された、第2の入出力端子と、前記第1の入出力端子と前記第2のウェル領域との間に接続された第1の容量素子と、前記第1の容量素子とグランド電位との間に接続された第2の容量素子と、を備えたことを特徴とするスイッチング装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】高性能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の一態様は、Si基板1a上に形成された絶縁層1bと、前記絶縁層上に形成された第1のSOI層1cと、前記第1のSOI層により形成されたバックゲート電極1c'と、前記バックゲート電極上に形成されたバックゲート絶縁層7aと、前記バックゲート絶縁層上に形成された第2のSOI層3と、前記第2のSOI層上に形成されたフロントゲート絶縁層と、前記フロントゲート絶縁層上に形成されたフロントゲート電極10と、前記第2のSOI層に形成されたソース領域及びドレイン領域それぞれの不純物層と、前記バックゲート電極に電気的に接続された第1の配線16aと、前記フロントゲート電極に電気的に接続された第2の配線16bと、を具備することを特徴とする半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】pチャネルトランジスタ及びnチャネルトランジスタの閾値電圧を共に低減できるCMISトランジスタを有する半導体装置を提供する。

【解決手段】pチャネルトランジスタは、半導体基板100における第1の領域上に形成された第1のゲート構造150Aと、第1のゲート構造150Aの側壁上に形成された第1のスペーサ構造とを有する。nチャネルトランジスタは、半導体基板100における第2の領域上に形成された第2のゲート構造150Bと、第2のゲート構造150Bの側壁上に形成された第2のスペーサ構造とを有する。第1のスペーサ構造における第1のゲート構造150Aの側壁との接触部分の含有酸素濃度は、第2のスペーサ構造における第2のゲート構造150Bの側壁との接触部分の含有酸素濃度よりも高い。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】p型MISトランジスタ及びn型MISトランジスタの特性を向上した相補型MISトランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、p型半導体領域10A及びn型半導体領域10Bを有する半導体基板101の上に、高誘電率膜106、アルミニウムからなる第1のキャップ膜107及びハードマスク108を順次形成する。次に、第1のキャップ膜107及びハードマスク108におけるn型半導体領域10Bの上に形成された部分を除去する。その後、半導体基板101の上に、実効仕事関数を低下させる効果を有する元素を含む第2のキャップ膜109を形成する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置、センスアンプ回路、半導体装置の制御方法及びセンスアンプ回路の制御方法

【課題】ダブルゲートトランジスタを用いた機能回路のバックゲート電圧を適切に制御して良好な特性を実現可能な半導体装置等及びその制御方法を提供する。

【解決手段】本発明の半導体装置は、ダブルゲートトランジスタを含む機能回路と、ダブルゲート構造の基準トランジスタ20、30を含む電圧制御回路を備えている。基準トランジスタ20、30には、第1ゲート電極に参照電圧Vrp、Vrnが印加され、第2ゲート電極の電位はドレイン電流Ip、Inが参照電流Irp、Irnと一致するように制御され、その電位が制御電圧VBGP、VBGNとして出力される。制御電圧VBGP、VBGNを機能回路のダブルゲートトランジスタの第2ゲート電極に印加することで機能回路に所望の特性が付与される。

(もっと読む)

電界効果型半導体装置

【課題】各種電子機器の中枢であるMOSFETの製造において,微細化技術に頼らない高性能化および超低消費電力化技術を提供する。

【解決手段】MOSFETに印加するゲート電圧に連動してゲート絶縁膜中の電荷分布を変化させ,半導体の表面電位を該ゲート電圧の極性とは反対の極性方向に変化させる機能を利用することによりしきい値電圧を低減し,低電圧動作および低消費電力化を可能にする。

(もっと読む)

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

101 - 120 / 743

[ Back to top ]