Fターム[5F048BB14]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521)

Fターム[5F048BB14]の下位に属するFターム

閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB14]に分類される特許

141 - 160 / 743

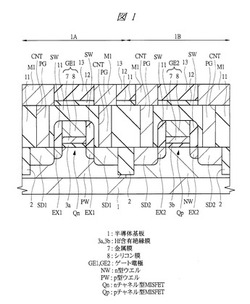

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置

【課題】しきい値電圧の制御にチャネルドープ法を用いて行う場合、活性層に不純物を導入するため、必然的にこの不純物起因のバルク結晶欠陥や、半導体層と絶縁層の界面凖位を生じさせてしまう。この結果、TFT特性、特に電界効果型移動度を悪化させる原因となる。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置

【課題】歪特性の改善が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1のFET103および第2のFET113のそれぞれに対応して設けられた基板電位制御用半導体層902および903と、半導体基板内に設けられ、基板電位制御用半導体層902および903のそれぞれを電気的に分離する素子間分離領域901と、基板電位制御用半導体層902および903のそれぞれに対応して設けられた第1の基板電位制御用電極108および第2の基板電位制御用電極118と、第1の基板電位制御用電極108および第2の基板電位制御用電極118のそれぞれに対応して設けられ、対応する基板電位制御用電極に高電圧又は低電圧を印加する複数の第1の基板電位制御信号源109および第2の基板電位制御信号源119とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子の小型化と電界効果トランジスタのラッチアップ耐性の向上とを両立させた半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板11のNウェル抵抗素子形成領域にSTI12を形成する。次に、P型MOSトランジスタ形成領域に対してドナーを注入して、ドナー拡散領域21を形成する。次に、Nウェル抵抗素子形成領域及びP型MOSトランジスタ形成領域に対してドナーを注入して、Nウェル抵抗素子形成領域におけるSTI12の直下域にN型ウェル14を形成すると共に、P型MOSトランジスタ形成領域にドナー拡散領域20を形成する。ドナー拡散領域21及び20は重ね合わせられて、P型MOSトランジスタ7のチャネル領域を構成するN型ウェル19が形成される。このとき、N型ウェル14及びドナー拡散領域20を形成するための不純物注入量を、ドナー拡散領域21を形成するための不純物注入量よりも少なくする。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

ハイブリッド半導体基板の製造プロセス

【課題】ハイブリッド半導体基板及びその製造方法を提供する。

【解決手段】本発明は、(a)ベース基板3の上の絶縁層5と絶縁層の上のSeOI層7とを備えるセミコンダクタ−オン−インシュレータ(SeOI)領域13と、バルク半導体領域11とを具備するハイブリッド半導体基板1を提供するステップであって、SeOI領域とバルク半導体領域とは同じベース基板を共用するステップと、(b)SeOI領域の上にマスク層9を提供するステップと、(c)SeOI領域とバルク半導体領域を同時にドーピングすることにより、第1の不純物レベルを形成するステップであって、このドーピングは、SeOI領域の第1の不純物レベルがマスク内に含まれるように実行されるステップとを含む方法に関する。それによって、ハイブリッド半導体基板の製造プロセスに、より多くのプロセスステップが含まれることを防ぐ。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】インバータ回路のスイッチング素子としてWBG半導体を用い、オン抵抗を低く保ちながら負荷短絡耐量が高い信頼性の高い半導体装置を得る。

【解決手段】インバータ回路のスイッチング素子に適用される半導体装置であって、半導体材料のバンドギャップがシリコンよりも広く、主トランジスタの短絡時の電流制限回路を有しており、電流を主に流すための主トランジスタと、該主トランジスタに並列に接続され主トランジスタに流れる電流に比例した微小電流を検知するセンストランジスタと、センストランジスタの出力に基づき主トランジスタのゲートを制御する横型MOSFETを同一半導体上に形成する。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体デバイス及びその製造方法

【課題】絶縁層を介して基板同士を貼り合わせることで、一方の基板上に形成された半導体層を他方の基板に形成できると共に、半導体層の結晶構造を損傷させることなく高品質に維持できる半導体デバイス及びその製造方法を提案する。

【解決手段】ECRプラズマを用いてIII−V族化合物半導体層7及びSi基板4上に酸化膜6a,6bを形成するようにしたことで、当該III−V族化合物半導体層7及び酸化膜6a,6bへのダメージが低減され、酸化膜6a,6bを平坦に形成できると共に、III−V族化合物半導体層7の結晶構造も損傷させることなく高品質に維持できる。これにより酸化膜6a,6bを介しSi基板4及びInP基板12同士を貼り合わせることで、一方のInP基板12上に形成されたIII−V族化合物半導体層7を他方のSi基板4に形成できると共に、III−V族化合物半導体層7の結晶構造を損傷させることなく高品質に維持できた半導体デバイス1を提案できる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体装置

【課題】FD型トランジスタで構成された電気回路において、電気回路に電力を供給する電源のスイッチングトランジスタを基板電圧で制御することができる半導体装置を提供する。

【解決手段】半導体装置は、基板上の第1のFinに形成された第1のトランジスタを含む電気回路と、半導体基板上の第2のFinに形成され、電気回路と電源供給線との間に接続された第2のトランジスタを含む電源回路と、基板に基板電圧を印加するための基板コンタクトとを備え、第1のFinの幅は、第1のトランジスタのチャネル部に形成される最大空乏層幅の2倍以下であり、第2のFinの幅は、第2のトランジスタのチャネル部に形成される最大空乏層幅の2倍よりも大きい。

(もっと読む)

サブスレッショルド集積回路におけるプロセスばらつき防止方法およびボディ電位変調回路

サブスレッショルド集積回路におけるプロセスばらつき防止方法とボディ電位変調回路が掲載されている。前記ボディ電位変調回路は、目標MOSデバイス(11)と、誘導MOSデバイス(12)と、電流−電圧変換回路(13)とを備えている。前記電流−電圧変換回路は、誘導MOSデバイスから出力された誘導電流を誘導電圧に変換するとともに、その誘導電圧を目標MOSデバイスのボディ端にフィードバックして、目標MOSデバイスのボディ電位を変調するためのものである。  (もっと読む)

(もっと読む)

半導体装置

【課題】保護回路において、所望の遅延時間を実現する。また、遅延回路の小型化を図り、消費電力を低減させる。

【解決手段】遅延回路100は、第1のインバータ101〜第3のインバータ103、第4のpチャネルMOSFET7、第4のnチャネルMOSFET8、遅延抵抗121およびキャパシタ122で構成されている。遅延抵抗121は、第1のインバータ101の出力端子と第2のインバータ102の入力端子の間に接続されている。第4のnチャネルMOSFET8のゲート端子は、遅延抵抗121と第2のインバータ102の入力端子の間のノード113に接続されている。第4のnチャネルMOSFET8のゲート端子とドレイン端子の間には、キャパシタ122が接続されている。第4のnチャネルMOSFET8の帰還容量を用いることで、キャパシタ122の容量を、キャパシタ122の物理的な静電容量よりも擬似的に大きくする。

(もっと読む)

電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられた絶縁ゲート電界効果トランジスタ(100)は、チャンネルゾーン(244)によって横方向に分離された一対のソース/ドレインゾーン(240及び242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーン上方でゲート誘電体層(260)の上側に存在している。各ソース/ドレインゾーンは、主要部分(204M又は242M)及び該主要部分と横方向に連続的であり且つ該ゲート電極下側を横方向に延在する一層軽度にドープした横方向延長部(240E又は242E)を包含している。該横方向延長部は、該チャンネルゾーンを上部半導体表面に沿って終端させており、異なる原子量の一対の半導体ドーパントによって夫々ほぼ画定される。該トランジスタが非対称的装置であり、該ソース/ドレインゾーンはソース及びドレインを構成する。該ソースの横方向延長部は該ドレインの横方向延長部よりも一層軽度にドープされており且つ一層高い原子量のドーパントで画定される。

(もっと読む)

ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造

【課題】 一群の高性能同極性絶縁ゲート電界効果トランジスタ(100,108,112,116,120及び124又は102,110,114、118,112及び126)が、アナログ及び/又はデジタル適用例用の広く多様なトランジスタを提供する半導体製造プラットフォームに適した横方向ソース/ドレイン延長部、ハローポケット、及びゲート誘電体厚さの選択可能な異なる構成を有している。

【解決手段】 各トランジスタは、一対のソース/ドレインゾーン、ゲート誘電体層、及びゲート電極を有している。各ソース/ドレインゾーンは主要部分及び一層軽度にドープした横方向延長部を有している。該トランジスタの内の一つのソース/ドレインゾーンの内の一つの横方向延長部が該トランジスタの別のもののソース/ドレインゾーンの内の一つの横方向延長部よりも一層高度にドープされており又は/及びそれよりも上部半導体表面下側により少ない深さに延在している。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

141 - 160 / 743

[ Back to top ]