Fターム[5F048BE04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077) | 同型多ウェル (525)

Fターム[5F048BE04]に分類される特許

21 - 40 / 525

半導体装置およびその製造方法

【課題】フォトダイオードを有する半導体イメージセンサーにおいて、より高い光検出効率を実現し、光検出部以外の信号処理を行う画素トランジスタの特性を安定させることで、半導体装置の微細化を可能にする。

【解決手段】フォトダイオードPDを構成するP+領域126およびN型領域111に炭素を共注入して炭素注入層128a、128bを形成することで、フォトダイオードPDの容量を増大させる。また、炭素注入層128bの形成によりN型領域111を含む転送トランジスタTrのチャネル内のホウ素の分布を均一化し、転送トランジスタTrの特性を安定させることで半導体装置内の素子の特性ばらつきの発生を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタの低濃度不純物拡散層がコンタミネーションから保護されて、半導体装置の特性を安定化できるようにする。

【解決手段】基板1の上に、ゲート絶縁膜3a及びゲート電極4aを順次形成し、ゲート電極4aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に低濃度不純物拡散層5aを形成する。続いて、ゲート電極4aの上から該ゲート電極4aの側方を通って低濃度不純物拡散層5aの上の一部までを連続して覆うように不純物拡散抑制膜7aを形成する。続いて、ゲート電極4a及び不純物拡散抑制膜7aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に、低濃度不純物拡散層5aよりも不純物濃度が高い高濃度不純物拡散層8aを形成する。その後に、不純物拡散抑制膜7aを残存させた状態で基板1に対して加熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

半導体装置

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置

【課題】 出力回路用、或いは、アナログ回路用の2種類の特性に夫々特性が最適化されてなるトランジスタを備えた半導体装置を低コストで提供する。

【解決手段】

同一基板101上に、出力回路用の第1のトランジスタ1aと、アナログ回路用の第2のトランジスタ1bが搭載された半導体装置であって、各トランジスタのゲート絶縁膜が、ドリフト領域107上面の一部の領域において、膜厚の厚い厚膜絶縁膜108bとなっており、ボディ領域103に向かって延伸するドリフト領域107を、第1のトランジスタ1aでは当該厚膜絶縁膜108bのボディ領域103側境界Aを超えて延伸させ、第2のトランジスタ1bでは当該厚膜絶縁膜108bのボディ領域側境界Aよりも内側にとどまるように延伸させる。

(もっと読む)

半導体装置

【課題】横型IGBTのコレクタ領域側にPN接合によりアバランシェダイオードをさらに設けることにより、ESD保護回路の面積および製造コストを減少させ、かつ、直流電流が重畳した場合にも素子破壊を防止するESD保護回路を含む半導体装置を提供する。

【解決手段】外部電圧を受ける第1のノードと、接地電圧を受ける第2のノードと、第1および第2のノードの間に並列に接続される保護回路および被保護素子を備え、保護回路は、エミッタが第2のノードに接続される横型IGBTと、アノードが横型IGBTのコレクタに接続され、カソードが第1のノードに接続されるアバランシェダイオードと、第1および第2のノードの間に接続され、横型IGBTのゲートに接続されるクランプ駆動回路とを含む。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

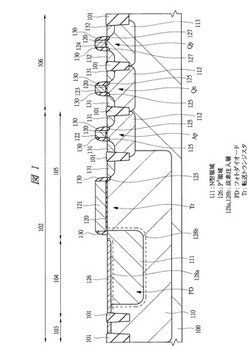

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図る。

【解決手段】ゲート電極GE1,GE2,GE3,GE4の側壁上にオフセットスペーサを形成した状態で半導体基板1のnMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれにイオン注入を行うことで、ソース・ドレインのエクステンション領域を形成する。この際、nMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれに対して別々のフォトレジストパターンを用いて個別にイオン注入を行うが、フォトレジストパターンを形成し直す度に、オフセットスペーサを形成し直すようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1導電型の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2導電型の不純物層及び第1のエピタキシャル半導体層とは膜厚の異なる第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上に第1のゲート絶縁膜と同じ膜厚の第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

21 - 40 / 525

[ Back to top ]