Fターム[5F058BH20]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成後の処理 (2,470) | その他 (240)

Fターム[5F058BH20]に分類される特許

1 - 20 / 240

成型材料および該材料を用いた成型体、ならびに該成型体の製造方法

【課題】金属酸化物薄膜パターンの形成に適した成型材料、及び当該材料を用いて成型体を製造する際の最適条件を提供すること。

【解決手段】本発明の成型材料は、金属アルコキシドのオリゴマーを含むことを特徴とする。

(もっと読む)

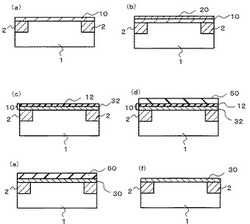

半導体装置の製造方法

【課題】金属膜あるいは金属酸化膜の成膜量に伴うことなく含有している金属元素の濃度分布に偏りのないゲート絶縁膜を提供する。

【解決手段】図2に示すように、半導体基板1上に、シリコン酸化膜より高い誘電率を有する高誘電体膜10を形成する高誘電体膜形成工程と、高誘電体膜10上に、第1の金属元素を有する第1の金属膜あるいは金属酸化膜20を成膜する第1の成膜工程と、高誘電体膜10に第1の金属元素を拡散させる拡散工程と、高誘電体膜10上に金属元素吸収膜50を成膜する第2の成膜工程と、金属元素吸収膜50に、第1の金属元素を含ませる吸収工程と、金属元素吸収膜60を選択的に除去する除去工程の6工程を含んでいる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

薄膜製造装置、該薄膜製造装置により製造した電気機械変換膜、電気機械変換素子、液滴吐出ヘッド及び液滴吐出装置

【課題】良質な薄膜を製造することができる。

【解決手段】液滴吐出ヘッド300によって基板11に吐出された機能性インク膜302にレーザ光を照射して加熱すると溶媒が蒸発して溶液が乾燥する。リアルタイムレーザ制御装置600によって機能性インク膜302の乾燥状態を検出する。そして、機能性インク膜302の乾燥状態に対する最適なレーザ光照射条件の関係の特性データと照合しながら検出した機能性インク膜302の乾燥状態に対応する最適なレーザ光照射条件を決定する。

(もっと読む)

薄膜製造装置及び薄膜製造方法

【課題】熱処理方法としてレーザーを使用して薄膜を製造する薄膜製造装置であって、最適なレーザー条件を算出、制御することができる薄膜製造装置を提供すること。

【解決手段】基板上に機能性インクを所定のパターンで塗布する塗布手段と、塗布された前記機能性インクを加熱して結晶化するための1つ又は2つ以上のレーザー光源と、前記機能性インクの結晶状態を測定するためのX線回折装置と、前記X線回折装置により測定された前記機能性インクの前記結晶状態の情報を記録する記録部と、前記レーザー光源のレーザー照射条件を制御する制御装置と、を有し、前記制御部は、前記記録部に記録された、事前の前記レーザー光源によるレーザー照射した前記機能性インクの前記結晶状態の情報に基づいて、前記レーザー光源のレーザー照射条件を調整するようにする、基板上に薄膜を形成する薄膜製造装置。

(もっと読む)

膜形成方法および膜形成装置

【課題】良質な膜を簡便に形成する膜形成方法および膜形成装置を提供することである。

【解決手段】実施形態の膜形成方法は、少なくとも1つの有機官能基と、加水分解を起こす1つの官能基と、を含む有機ケイ素化合物を、大気雰囲気において基板の表面に供給する第1の工程と、前記有機ケイ素化合物を前記基板の前記表面に供給後、前記有機官能基を酸化し、前記基板の前記表面上にケイ素と酸素とを含む層を形成する第2の工程と、を備える。

(もっと読む)

低反射基板の製造方法、および光起電力装置の製造方法

【課題】短時間のエッチングで低反射化が可能な低反射基板の製造方法を得る。

【解決手段】低反射基板の製造方法は、(100)単結晶シリコン基板1aを挟んだ両面の上に不純物拡散層2を形成する工程と、両面に形成された不純物拡散層の上に50nm以上400nm以下の膜厚のシリコン酸化膜3を形成する工程と、一方の上のシリコン酸化膜に対してブラスト加工を施すことにより、シリコン酸化膜を貫通して不純物拡散層に達する開口4を形成する工程と、基板をシリコン酸化膜が耐性を有するアルカリ水溶液に浸漬して開口を介したアルカリ水溶液による不純物拡散層のエッチングを行うことにより、シリコン酸化膜と基板との間にアンダーカットを形成する工程と、引き続きアルカリ水溶液により、アンダーカットの空間的な広がりに依存しつつシリコン(111)面を露出させる異方性エッチングを行う工程と、その後にシリコン酸化膜を除去する工程とを含む。

(もっと読む)

強誘電体膜の作製方法

【課題】 良好な規格化保持時間を有するエピタキシャル成長させて得られた強誘電体膜の作製方法を提供すること。

【解決手段】 チタン酸ストロンチウム単結晶基板又はシリコン単結晶基板上に、電極層を介して、強誘電体膜をエピタキシャル成長させて形成し、次いでエピタキシャル成長させて形成された強誘電体膜を冷却する強誘電体膜の作製方法において、この冷却を、少なくとも冷却を開始した後から該強誘電体のキュリー温度より15%高い温度〜15%低い温度の範囲までの冷却速度をその範囲の温度から室温までの冷却速度より遅くして実施する第1冷却工程と、次いで該第1冷却工程の冷却速度より早い冷却速度で室温まで冷却する第2冷却工程とで実施する。

(もっと読む)

膜形成方法および膜形成装置

【課題】担持体上に形成したポリシラザン膜を転写することにより、基板表面に良好な膜を形成することのできる技術を提供する。

【解決手段】ポリシラザン材料を含む塗布液が表面に塗布されてなる薄膜Rを担持するシートフィルムFを処理チャンバ1内に収容し、処理チャンバ1内を排気する。加熱ヒータ541によってシートフィルムFを所定温度に加熱しつつ、処理チャンバ1内に酸素を含む硬化促進ガスを導入して薄膜Rの粘度を増大させる。その後、ガスの供給を停止するとともに処理チャンバ1内を再び排気することで硬化促進ガスを除去し、硬化の進行を抑制する。この状態で、シートフィルムF上の薄膜Rと基板Wとを密着させ加圧することで、薄膜Rを基板Wに転写する。

(もっと読む)

光学素子およびその製造方法

【課題】サイズが小さくなっても、受光部などの光学領域への集光を向上させることが可能な光学素子を提供する。

【解決手段】光学領域(フォトダイオードである受光部102)を有する半導体基板101と、半導体基板101の上に配置された透明絶縁膜111を有し、透明絶縁膜111は、光学領域直上の第1の領域(遮光膜110によって挟まれる領域)と、第1の領域の上の第2の領域を有し、透明絶縁膜111は、第2の領域と同じ高さにあり、平面視において第2の領域の外側に位置する第3の領域(遮光膜110の上の領域)を有し、第1の領域が有する空孔115の空孔径は第3の領域が有する空孔115の空孔径よりも小さい。

(もっと読む)

金属酸化物膜の製造方法及び製造装置

【課題】強誘電体等からなる金属酸化物膜を所望の位置に低温で低コストで形成する。

【解決手段】金属酸化物膜を形成するための前駆体溶液に、金属酸化物膜が成膜される基板を浸す工程と、前記基板と前記前駆体溶液との界面に光を集光した状態で、前記光を走査しながら照射する工程と、を有し、前記前駆体溶液は前記光を透過するものであって、前記基板上に前記金属酸化物膜を形成することを特徴とする金属酸化物膜の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを覆うシリコン窒化膜を用いて、該トランジスタの駆動能力をより一層向上することができるようにする。

【解決手段】Pウェル102の上に、NMOSゲート絶縁膜104を介在させて形成されたNMOSゲート電極106と、Pウェル102におけるNMOSゲート電極106の両側方の領域に形成されたn型ソースドレイン領域112と、Pウェル102の上に形成され、NMOSゲート電極106及びn型ソースドレイン領域112を覆うように形成されたシリコン窒化膜118とを有している。シリコン窒化膜118を構成するシリコンは、その同位体29Si又は30Siの比率が50%以上である。

(もっと読む)

半導体基板の酸化膜の形成方法、及び半導体基板の不純物分析方法

【課題】半導体基板のごく表層部の不純物分析を、高感度かつ高精度に実施することのできる、半導体基板の酸化膜の形成方法、及び半導体基板の不純物分析方法を提供する。

【課題を解決するための手段】アンモニア溶液の液面に対して、半導体基板の一主面を並行に対向させて配置し、前記アンモニア溶液の液面と前記半導体基板の一主面との距離が均等になるように保持した状態で、常温下にて放置することを特徴とする半導体基板の酸化膜形成方法であり、さらに、半導体基板の一主面はシリコン、窒化ガリウムのいずれかで構成されていること、アンモニア溶液の液面と半導体基板の一主面との距離が3mm以上20mm以下、放置時間が60分以上400分以下であること、アンモニア溶液の濃度が15重量%以上35重量%以下であることが望ましい。

(もっと読む)

薄膜形成装置の洗浄方法、薄膜形成方法、薄膜形成装置及びプログラム

【課題】効率的に薄膜形成装置を洗浄することができる薄膜形成装置の洗浄方法等を提供する。

【解決手段】まず、反応管2にフッ化水素を含むクリーニングガスを供給して、装置内部に付着した付着物を除去する。次に、反応管2に酸素ラジカルを供給して装置内部に付着した珪フッ化物を酸化する酸化工程を実行する。続いて、反応管2にフッ化水素を含むクリーニングガスを供給して酸化された珪フッ化物を除去する酸化物除去工程を実行する。そして、この酸化工程と酸化物除去工程とを複数回繰り返す。これにより、効率的に薄膜形成装置1が洗浄される。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

基板上の堆積層を硬化させるシステム及び方法

【課題】印刷したエレクトロニクスの簡略化した製造、処理量、装置のコスト及び寸法の軽減、必要な硬化エネルギの量の減少、硬化過程中に放出される揮発性有機化合物減少を実現する硬化方法及びシステムを提供する。

【解決手段】少なくとも1つの堆積層を有する基板を支持する平坦な支持面と、少なくとも1つの堆積層を硬化させる少なくとも1つの硬化装置と、全体的な硬化過程を制御する制御システムとを含む硬化システムが提供される。硬化装置は、少なくとも1つのレーザと、レンズモジュールと、選択随意的な変調器とを含む。硬化する間、レーザから放出された光ビームは、1)レーザ光の焦点合わせしたビームを堆積層の所望の照射領域まで導くようにX−Yビームの偏向モジュールの位置を制御すること、2)レーザの位置をX−Yテーブルを介して制御すること、又は3)基板の位置をX−Yテーブルを介して制御することにより堆積層に向けることができる。

(もっと読む)

圧電セラミックス膜形成用組成物、圧電素子の製造方法及び液体噴射ヘッドの製造方法

【課題】環境負荷が小さく且つクラックの発生が抑制された圧電セラミックス膜を形成することができる圧電セラミックス膜形成用組成物、圧電素子の製造方法及び液体噴射ヘッドの製造方法を提供する。

【解決手段】圧電セラミックス膜形成用組成物は、カリウム、ナトリウム、及びニオブを含む金属錯体混合物と、シリコーンオイルと、溶媒と、を含み、金属錯体混合物と溶媒との総量100容量部に対してシリコーンオイルを5容量部以下含む。所定量のシリコーンオイルを含むことにより、圧電セラミックス膜を形成する際の焼成工程における熱膨張が抑制されて、圧電セラミックス膜の残留応力を低減させることができる。これにより、クラックの発生が抑制されたニオブ酸カリウムナトリウム系の圧電材料からなる圧電セラミックス膜を形成することができるものとなる。さらに、鉛の含有量を抑えられるため、環境への負荷を低減することができる。

(もっと読む)

配線層の形成方法及び半導体装置の製造方法

【課題】配線層の表面の平坦度を高めることができ且つ配線間隔が広い領域において磁界を変動させる構成を無くした配線層の形成方法及び半導体装置の製造方法を提供する。

【解決手段】配線層の形成方法は、下側部材上に配線パターン102を形成する工程と、その上に絶縁材料層103,106を形成する工程と、配線パターンの間に形成された絶縁材料層の一部を、絶縁膜ブロック111として残すと共に、絶縁膜ブロック111の高さを、絶縁膜ブロック以外の絶縁材料層の高さより高くなるように、絶縁材料層をエッチング処理する工程と、絶縁膜ブロックを含む絶縁材料層を研磨して、表面が平坦化された層間膜を形成する工程とを有する。半導体装置の製造方法は、半導体基板と配線層とを有し、上記配線層の形成方法を用いて配線層の少なくとも1つを製造する。

(もっと読む)

トレンチ埋め込み方法、及びトレンチ埋め込み用組成物

【課題】高アスペクト比のトレンチ内に埋め込んだ際に、クラック、及びボイドが生じにくく、かつ高密度に埋め込むことができるトレンチ埋め込み方法。

【解決手段】(1)トレンチ2を有する基体1上に、シロキサン系重合体、空孔形成剤、及び有機溶媒を含むトレンチ埋め込み用組成物を、少なくとも該組成物が前記トレンチ内に充填されるように塗布し、塗膜3を形成する工程、及び、(2)工程(1)で得られた塗膜3に加熱処理および光処理の少なくともいずれか一方を行う工程、を含むトレンチ埋め込み方法。

(もっと読む)

エッチングで形成された溝を用いて厚い誘電体領域を形成する方法

【課題】エピタキシアル沈着工程だけを用いて製造される縁部端子領域を有する高電圧半導体ディバイスを提供すること。

【解決手段】半導体ディバイスの製造方法は相互に対向する第1及び第2の主表面を有する半導体基板を設けることを含む。この方法は、上記の半導体基板に少なくとも1つの溝と、第1メサおよび第2メサとを設けることを含む。この方法は、また、各溝の両側壁と底部とを酸化し、ドープされた酸化物を各溝ならびに第1および第2メサの頂部に沈着させて、沈着せられた酸化物が流動して、各第1メサのシリコンが完全に二酸化ケイ素に変換し、各第2メサのシリコンが部分的にのみ二酸化ケイ素に変換し、各溝には酸化物が充填される温度で、半導体基板を熱酸化させることを含む。

(もっと読む)

1 - 20 / 240

[ Back to top ]