Fターム[5F064EE32]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713)

Fターム[5F064EE32]の下位に属するFターム

Fターム[5F064EE32]に分類される特許

41 - 60 / 366

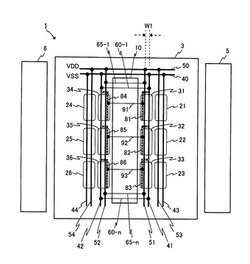

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置

【課題】面積を抑えたアンチヒューズ素子を備えた半導体装置を提供する。

【解決手段】半導体装置は、基板10と、第1絶縁膜11と、シリサイド膜12bを含む導電膜12と、コンタクト15と、を具備する。第1絶縁膜は、基板上に形成されている。導電膜は、第1絶縁膜上に形成されている。コンタクトは、基板上に形成され、第2絶縁膜14を介して導電膜に隣接して配置され、シリサイド膜と短絡している。

(もっと読む)

半導体装置

【課題】信頼性の高いヒューズを有する半導体装置を提供する。

【解決手段】半導体層22と、この半導体層22の表面に形成され、半導体層22と金属とが反応して形成された化合物層28,29と、半導体層22及び化合物層28,29から成るヒューズと、このヒューズの接地電位側に電気的に接続された、選択トランジスタ11とを含む、半導体装置を構成する。

(もっと読む)

銅技術相互接続構造を使用する集積回路デバイス用のアルミニウム・パッド電力バスおよび信号ルーティング技術

【課題】電力バス相互接続構造の工程数を低減して製造できる半導体装置の製造方法を提供する。

【解決手段】第1のパッシベーション・スタック149を、導電性ランナ132、134および誘電体層162の上に形成する。開口を、通常のリソグラフィ技術および誘電エッチング技術によって、第1のパッシベーション・スタックを貫通して画定し形成する。露出された表面上に導電性バリア層166を形成する。アルミニウム層をブランケット堆積して、開口を充填する。パターニング、エッチング工程によって、開口内に、アルミニウム・パッド170を形成する。開口内に、ランナ134と導電性接触する導電性バイア172を形成する。アルミニウム・パッドを形成するために用いられるのと同じパターニング、エッチング工程において、アルミニウム層内に電力バス174も形成する。

(もっと読む)

半導体装置のレイアウト方法及びその半導体装置

【課題】トランジスタのしきい電圧の変化を減らすことにより、半導体装置の信頼性を向上させることができる半導体装置のレイアウト方法及びその半導体装置を提供する。

【解決手段】半導体基板内に形成された少なくとも1つの第1電極と第2電極を有する複数個のトランジスタのアクチブ領域を配置する段階と、前記複数個のトランジスタのアクチブ領域のそれぞれの少なくとも1つの第1電極と第2電極との間に位置し、前記半導体基板上に所定の幅と長さを有する1つ以上の実質的に同一間隔に分離された前記複数個のトランジスタのゲートを配置する段階と、前記複数個のトランジスタの間に、所定の幅と長さを有し、前記半導体基板上に前記複数個のトランジスタの分離されたゲートの間隔と実質的に同一間隔に配置された複数個のダミーゲートを配置する段階とを有する。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

情報処理装置、プログラム、および設計支援方法

【課題】設計対象の集積回路内での回路特性のばらつきに伴う遅延時間の変動を反映したタイミング解析技術を提供する。

【解決手段】情報処理装置は、複数の回路素子を含む対象経路の信号伝搬時間を変化させる物理特性値を所定の変動範囲で複数個発生させる物理特性値発生部と、発生させた物理特性値にしたがって、回路素子を通る信号の遅延時間を算出する素子遅延算出部と、信号の遅延時間を基に対象経路の信号伝搬時間を算出する伝搬時間算出部と、を備える。

(もっと読む)

半導体装置

【課題】低消費電力かつ低占有面積で、パッケージ実装後においてもプログラムを行なうことができるヒューズ素子を備えるヒューズプログラム回路を実現する。

【解決手段】ヒューズプログラム回路(FPK1−FPKn)において、ヒューズ素子FSを、多層メタル配線の第3層以上のメタル配線(M(i))を用いて実現する。各ヒューズプログラム回路において、スキャンフリップフロップ(FSSRおよびPSR)を用いてプログラム情報およびヒューズ選択情報を順次転送して、選択的に、1本ずつヒューズを電気的に切断する。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

パワーグリッド最適化

【課題】導電材料の第1の層と導電材料の第2の層とを備える集積回路におけるグローバル電源配電網の最適化

をはかる。

【解決手段】パワーメッシュ配線を構成する、第1のレールは、(a)集積回路のコアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第1の軸に対して位置合わせされ、(c)メッシュが第1の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成される。また、第2のレールは、(a)コアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第2の軸に対して位置合わせされ、(c)メッシュが第2の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成された1つ以上のパラメータを有したものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

データ生成方法

【課題】エッチング処理により基板上に設計データ通りの配線パターンを形成できるようにする、レジストパターンのデータを生成するデータ生成方法を実現する。

【解決手段】レジストパターンのデータ生成方法は、基板面に相当する仮想平面上において、設計データに規定された配線の外郭上の或るポイントを基準点として所定形状を有し、当該ポイント上に位置するエッチング液によって銅箔がエッチングされ得るエッチング影響エリアを含む第1の基準エリアを設定する設定ステップS101と、レジストパターンの外郭の位置を、第1の基準エリアに占めるエッチング影響エリアの面積を表わすエリア面積パラメータに応じて決定する決定ステップS102と、設計データに規定された配線の外郭上の任意の位置に順次設定されるポイントに対して設定ステップS101および決定ステップS102を繰り返し実行することで、レジストパターンの外郭を画定する画定ステップS103と、を備える。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

41 - 60 / 366

[ Back to top ]