Fターム[5F064EE32]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713)

Fターム[5F064EE32]の下位に属するFターム

Fターム[5F064EE32]に分類される特許

61 - 80 / 366

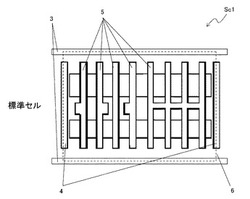

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体装置の配線抵抗算出装置

【課題】配線に多数のスルーホールが存在する場合にも、多数のスルーホール分割要素に分割されることを回避し、分割要素の数の増大を抑制し、配線抵抗の算出時間を短縮する装置の提供。

【解決手段】第1配線層と第2配線層の配線を接続する複数のスルーホールを有する領域に、複数のスルーホールを含む枠図形FF1を設定し、枠図形を複数の枠領域FR1〜3に分割する。各枠領域内の複数のスルーホールを合成して1つのスルーホールにまとめ、各枠領域内にはそれぞれ1つの合成スルーホールCT1〜3が設定される。各枠領域に1つに設定されたスルーホールの位置を基準として、第1配線層、第2配線層における枠図形に対応する配線抵抗を分割した抵抗値RL11〜14、RL21〜22と、各枠領域内で1つに設定されたスルーホールの抵抗値RCT1〜3とを用いて、抵抗回路網を作成し、抵抗回路網を1つの抵抗RSに合成する。

(もっと読む)

半導体デバイス及びマスク設計方法

【課題】アクティブフィーチャの容量カップリングを低減する。

【解決手段】本発明は、研磨ダミーフィーチャパターンの無差別な配置ではなく、研磨ダミーフィーチャパターンの選択的な配置を使用する。トポグラフィ変化の低周波数(数百ミクロン以上)及び高周波数(10ミクロン以下)の両方が検討された。研磨ダミーフィーチャパターンは半導体デバイス及び半導体デバイスの作製に使用される研磨条件に特に適合されている。集積回路をデザインする場合にはアクティブフィーチャの研磨効果が予測可能である。研磨ダミーフィーチャパターンが例図とに配置された後、局部的な(デバイスの全てではなく一部)レベルにおいて、及びさらに広域的なレベル(全デバイス、デバイスとは、レチクルフィールド、或いはさらにはウェハ全体に対応する)平坦性が検査される。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

半導体装置およびその製造方法

【課題】Cuを主成分とする材料からなる最上層配線からのパッシベーション膜の剥離を防止することができる、半導体装置を提供する。

【解決手段】半導体装置1は、層間絶縁膜26と、絶縁材料からなり、層間絶縁膜26上に形成されたパッシベーション膜33と、銅を主成分とする材料からなり、層間絶縁膜26の表面とパッシベーション膜33との間に形成された最上層配線28と、アルミニウムを主成分とする材料からなり、パッシベーション膜33と最上層配線28の表面との間に介在され、最上層配線28の表面を被覆する配線被覆膜31とを含む。

(もっと読む)

半導体装置

【課題】ゲート引き込み配線の長さが長く、ゲート引き込み配線に接続できる信号線の本数を十分に確保された半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1の方向に並置された複数の回路セルであって、それぞれはその方向と略直交する第2の方向に並置された第1の導電型の第1の領域と第2の導電型の第2の領域とに分離される複数の回路セルと、第2の方向に平行離間して配置すると共に第1の方向に延伸する第1の電源線及び第2の電源線とを備え、第1の領域は第1の電源線から第1の電源電位が供給される少なくとも一の第1のトランジスタを有し、第2の領域は第2の電源線から第2の電源電位が供給される少なくとも一の第2のトランジスタを有し、複数の回路セルのうちの少なくとも1つの回路セルはさらに第1の領域において第1及び第2のトランジスタの間に第1の容量素子を有することを特徴とする。

(もっと読む)

半導体装置

【課題】スタンバイ電流を低減したい回路ブロックに電流の供給を制御するスイッチ回路のレイアウト面積を抑制する。

【解決手段】半導体基板上に、第1方向に延伸する第1及び第2電源線で、第1及び第2電源線は第1方向に直交に配置され、第1電源線に第1電源電位が供給され、第2電源線に第2電源電位が供給される第1及び第2電源線と、第1方向に延伸し、第2方向に配置された第3電源線と、アクティブ時に第1及び第2電源電位の間の第1電源電圧で動作する回路ブロックで、複数の第1導電型の第1トランジスタと複数の第2導電型の第2トランジスタを備え、複数の第1トランジスタの少なくとも1つは第3電源線に接続される回路ブロックと、第1電源線と第3電源線の間に接続され、回路ブロックがアクティブ状態のとき第1及び第3電源線を導通状態として第3電源線に第1電源電位を供給し、スタンバイ状態のとき第1及び第3電源線とを非導通状態とする第3トランジスタとを有する。

(もっと読む)

半導体装置

【課題】配線効率が向上した半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1の配線層と、その上方に形成された第2の配線層と、第2の配線層で第1の方向に平行離間して形成されると共にその方向に略直交する第2の方向に延在する第1及び第2の電源線で、第1及び第2の電源線には第1の電源電位が供給され、第1の電源線は第1のトランジスタの上方に配置してその第1の拡散層に接続され、第2の電源線は第2のトランジスタの上方に配置してその第1の拡散層に接続されている第1及び第2の電源線と、第1のトランジスタの第2の拡散層と第2のトランジスタの第1のゲート電極との間、又は、第1及び第2のトランジスタの第1のゲート電極の間のいずれか一方に配置された信号経路であって、信号経路は第1及び第2の電源線の間に第2の配線層に形成された第1の部分を含む信号経路とを備えたことを特徴とする。

(もっと読む)

配線構造

【課題】クラックからの水分侵入に起因する金属配線端面の腐食防止、あるいは金属配線端面の腐食が生じている場合でも該腐食が液晶表示装置を駆動する液晶表示部分を構成するゲート線等の金属配線にまで到達することを防止する技術を提供する。

【解決手段】基板の上に、複数の金属配線が同一平面上に形成され、金属配線の上に絶縁膜が形成された積層構造を有し、切り出し加工により切断端面が露出している第1の金属配線を有する配線構造であって、

第1の金属配線の線幅をX(μm)、

第1の金属配線の長さをY(μm)としたとき、

(1)若しくは(2)、および/または下記(3)の要件を満足することを特徴とする配線構造。

(1)X≦20μm

(2)X>20μmのときは、Y≧10X−160、

(3)第1の金属配線の切断端面から、第1の金属配線に隣接する第2の金属配線までの間において、第1の金属配線は絶縁膜の存在しない領域Zを有する。

(もっと読む)

電流ヒューズ、半導体装置及び電流ヒューズの切断方法

【課題】ヒューズ部を容易に切断する。

【解決手段】基体上に設けられるヒューズ部20と、前記ヒューズ部20の上層又は前記基体と前記ヒューズ部20の間の下層に配置され、かつ前記ヒューズ部20が通電した際に、前記ヒューズ部20の一部分と同電位となり、前記ヒューズ部20の一部分側から、前記一部分と相違する電位となる前記ヒューズ部20の他の部分の上層又は下層まで延在する導電部16と、を備える。

(もっと読む)

半導体装置

【課題】チップ面積を増加させずに、半導体チップの主面上に占める配線領域を拡大する。

【解決手段】半導体チップの主面上に形成された例えばMISトランジスタなどを含んで構成される内部回路7から、例えばダイオードからなる保護素子11および保護素子12に電気的に接続する信号配線8を保護素子11と保護素子12との間の配線13上の取り出し口29から引き出して、信号配線8が占める信号配線領域10を、保護素子12上および電極パッド9下に設ける。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

アンチヒューズ構造およびアンチヒューズ構造の製造方法

【課題】低い印加電圧(3V以下)で導通状態を変更可能なアンチヒューズ素子(アンチヒューズ構造)を提供する。

【解決手段】本発明のアンチヒューズ構造100は、第一配線3と、前記第一配線3上に順次積層された、不純物を含有した第一の多結晶シリコン膜6、第一のタングステンシリサイド膜7、第一の窒化タングステン膜8からなる第一のアンチヒューズ部20aと、前記第一のアンチヒューズ部20a上に接続された第二配線10と、を具備してなることを特徴とする。

(もっと読む)

半導体集積回路のレイアウト設計装置及び方法

【課題】機能マクロの内部配線と電源端子との間に生じる寄生容量を小さくすることができる半導体集積回路のレイアウト設計装置及びレイアウト設計方法を提供する。

【解決手段】半導体集積回路のレイアウト設計方法は、第1メタル層として半導体素子、第2メタル層として内部配線、第3メタル層として帯状の電源端子を有する機能マクロを半導体集積回路上に配置し、半導体集積回路の配置結果情報及び機能マクロの情報が登録されたライブラリを参照して前記機能マクロの配置方向を判定し、機能マクロが基本の状態から90度回転していると判定した場合は、電源端子に接続する、第4メタル層となる電源接続配線を、その長手方向が前記電源端子に重なるように配置し、電源接続配線上に当該電源接続配線と直行する方向に第5メタル層となるメッシュ状電源配線を配置する。

(もっと読む)

半導体装置及び半導体装置のレイアウト設計方法

【課題】アナログ回路に利用される抵抗素子の配置領域面積を低減し、抵抗素子の相対精度を向上させる半導体装置及び半導体装置のレイアウト設計方法を提供する。

【解決手段】一の方向に並列配置されたトランジスタ素子(トランジスタ素子Q1及びトランジスタ素子Q2)と、トランジスタ素子上に層間絶縁膜(層間絶縁膜14)を介して形成された抵抗素子(抵抗素子R1及び抵抗素子R2)を有し、平面視において抵抗素子の長さ方向はトランジスタ素子のチャネル幅方向に直交する。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電気ヒューズに電流を流したときの被切断部の発熱を大きくして、電気ヒューズを切断しやすくする。

【解決手段】半導体装置100は、基板101上に形成された層間絶縁膜108と、層間絶縁膜108中に形成された第1の配線120により構成され、被切断部152を有する電気ヒューズ150と、第1の配線120と同層において、被切断部152の両側方に、それぞれ、被切断部152に沿って延在して形成された第2の配線126および第3の配線128と、を含む。ここで、被切断部152と第2の配線126との間、および被切断部152と第3の配線128との間には、それぞれ、被切断部152に沿って延在して形成されたエアギャップ118が設けられている。

(もっと読む)

61 - 80 / 366

[ Back to top ]