Fターム[5F064EE32]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713)

Fターム[5F064EE32]の下位に属するFターム

Fターム[5F064EE32]に分類される特許

81 - 100 / 366

半導体集積回路装置およびその製造方法、配線配置装置、配線配置方法、配線配置プログラム、並びに記録媒体

【課題】スタンダードセルを利用して機能回路ブロックをレイアウトする際、供給電源の品質を動作レベルに保ちながら、製造品質を左右する各配線層の占有率のばらつきを少なくする。

【解決手段】スタンダードセル1を、これを構成するセル構成トランジスタを有し、全スタンダードセルに共通接続される電源供給配線及び接地供給配線、および個々のスタンダードセルの機能を実現するための信号配線を含まず、かつ各スタンダードセルの機能を該セル構成トランジスタにより決定する最小限の配置配線、および該セル構成トランジスタの直近に配置され、該スタンダードセルの信号端子を含むよう構成した。

(もっと読む)

無線集積回路装置の製造方法、無線集積回路装置及び電子機器

【課題】効率的な動作試験ができる無線集積回路装置の製造方法、無線集積回路装置及び電子機器等を提供すること。

【解決手段】無線集積回路装置の製造方法は、ウェハー上に複数の無線集積回路装置100を形成し、複数の無線集積回路装置100のうちの少なくとも1つの無線集積回路装置を送信モード無線集積回路装置100aに設定し、複数の無線集積回路装置100のうちの送信モード無線集積回路装置100aを除く少なくとも1つの無線集積回路装置を受信モード無線集積回路装置100bに設定する。送信モード無線集積回路装置100aの送信回路により動作試験用の送信データを送信し、受信モード無線集積回路装置100bの受信回路により動作試験用の送信データを受信して動作試験を実行する。動作試験の完了後に複数の無線集積回路装置100をダイシングする。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

半導体装置及びその設計方法並びに半導体装置の製造方法

【課題】良好な電気的特性を有する半導体装置及びその設計方法並びに半導体装置の製造方法を提供する。

【解決手段】第1のトランジスタが形成される第1の活性領域のパターンと、第2のトランジスタが形成される第2の活性領域のパターンとを配置するステップS2と、第1の活性領域及び第2の活性領域と交差するゲート配線のパターンを配置するステップS3と、第1の活性領域とゲート配線とが重なり合う領域である第1の領域を抽出するステップS4と、第1の活性領域を含む領域上に、圧縮応力膜のパターンを配置するステップS5とを有し、第2の活性領域を含む領域上に、圧縮応力膜に隣接する引っ張り応力膜のパターンを配置するステップS6とをコンピュータに実行させることにより、半導体装置のレイアウトパターンを取得する工程を有し、圧縮応力膜のパターンを配置するステップでは、第1の領域の縁部の位置に基づいて、圧縮応力膜のパターンの縁部の位置が設定される。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】半導体抵抗素子102と、半導体抵抗素子102の端子部上に、半導体抵抗素子102の幅方向と長手方向とにそれぞれ等間隔に配置された複数のコンタクトCTと、複数のコンタクトCT上に形成された配線101と、を備えた半導体回路のシミュレーション方法。1つのコンタクトCTの抵抗値と、長手方向において隣接するコンタクトCT間の半導体抵抗素子102による寄生抵抗値との比を、定数kとして定義し、半導体抵抗素子102の端子部と、複数のコンタクトCTと、を含む寄生抵抗ネットを、定数kを用いることによりモデル化する。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】溝内に配線を埋め込む際に層間絶縁膜の表面に深い凹部が生じるのを防止し得る半導体装置の設計方法等を提供する。

【解決手段】単位面積当たりの配線パターンの周囲長の総和を各々の単位領域毎に算出するステップS6と、単位領域内における配線パターンの周囲長の総和が第1の値以上である第1の領域と第2の値以下である第2の領域とを抽出するステップS7,S8と、第1の領域に隣接する第3の領域内に単位面積当たりの周囲長の総和が第3の値である第1のダミーパターンを配置し、第2の領域に隣接する第4の領域内に単位面積当たりの周囲長の総和が第4の値である第2のダミーパターンを配置するステップS9,S10と、第3の領域と第4の領域との間の第5の領域内に単位面積当たりの周囲長の総和が第3の値より小さく、第4の値より大きい第5の値である第3のダミーパターンを配置するステップS11とを有している。

(もっと読む)

半導体装置

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンチヒューズ素子が導通状態の際に形成される導電パスの電気抵抗を低くし、また、抵抗値のばらつきを抑制することができる半導体装置を提供する。

【解決手段】アンチヒューズ素子4を備えた半導体装置1であって、前記アンチヒューズ素子4は、半導体基板5に設けられたウェル41と、前記ウェル41上に設けられた絶縁膜42と、前記絶縁膜42上に設けられ、前記ウェル41と同じ導電型のポリシリコン膜43と、前記ウェル41内の一面41a側に設けられた、前記ウェル41と同じ導電型の不純物導入領域46とを備え、前記不純物導入領域46の不純物濃度が、前記ウェルの不純物濃度よりも高く、前記不純物導入領域46は、前記ポリシリコン膜43の前記ウェル41上に位置する端部と前記絶縁膜42を介して対向する部分を備えていることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

多層配線、多層配線のダミー配線配置方法、半導体装置およびその製造方法

【課題】層間絶縁膜のグローバル段差をより低減する。

【解決手段】メタル配線11、21、31と層間絶縁膜12、22、32とが積層され、各層の層間絶縁膜を形成する毎に研磨して平坦化される多層配線60を積層方向からみて複数の領域52に分割し、領域毎に、各領域の面積に対する各領域内のメタル配線の占有面積の割合を、メタル配線についてそれぞれ求め、求めた割合を、領域毎に、メタル配線について積算した積算割合をそれぞれ求め、複数の領域の積算割合を用いて、予め求めておいた積算割合の相対値と層間絶縁膜32の上面の相対位置との関係より、複数の領域間の層間絶縁膜32の上面の相対位置関係を求め、層間絶縁膜32の上面が所定の値より低い位置にある領域511では、ダミー配線13,23,33を設け、層間絶縁膜32の上面が所定の値以上の位置にある領域513ではメタル配線にダミー配線を設けない。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】高速動作が可能で、しかも可逆的に安定した書き換え特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供を目的とする。

【解決手段】第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備えている。この抵抗変化層104は少なくともハフニウム酸化物を含み、当該ハフニウム酸化物をHfOxと表した場合に、0.9<x<1.6を満足するように抵抗変化層104が構成されている。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

配線設計方法および配線設計装置

【課題】対向する金属配線を有する配線構造において特性の安定化や性能の向上を図ると共に高耐圧化を実現する。

【解決手段】配線設計装置は、対向する金属配線間に与えられる最大の電位差をVmaxとしたときに配線間距離dminを与える関係式Vmax=A×ln(dmin/d0)+B(A,Bは定数、d0は基準となる距離)を予め記憶する記憶部1と、金属配線間の距離を、想定される最大電位差Vmaxに対してVmax=A×ln(dmin/d0)+Bにより得られる配線間距離dmin以上として設定する設計部2とを備える。

(もっと読む)

半導体集積回路のレイアウト検証方法、設計方法、レイアウト設計プログラム、半導体集積回路の製造方法

【課題】レイアウト検証の時間を短縮し、設計TATを改善する。

【解決手段】本発明によるレイアウト検証方法は、記憶装置内に記録されたレイアウト情報201に基づいて、ゲート電極に接続される金属配線の面積を算出するステップと、レイアウト情報201に基づいて、金属配線に対してゲート電極と並列接続される拡散層の面積を算出するステップと、ゲート電極の面積を使用せず、金属配線の面積と拡散層の面積を用いて第1アンテナ比を算出するステップと、記憶装置内に記録されたアンテナ基準202に基づいて第1アンテナ比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体装置の設計方法

【課題】配線層の溶出、および酸化を抑制する半導体装置、およびその設計方法を提供する。

【解決手段】接続コンタクトに接続される金属配線の配置を決定するステップと、接続コンタクトを設けるためのスルーホールの配置を決定するステップとを具備する半導体装置に設計方法を適用する。ここで、金属配線の配置を決定するステップは、(a)スルーホールによって露出する金属配線の領域を特定するステップと、(b)金属配線に付帯する容量を特定するステップと、(c)容量が蓄える電荷が、領域を介して金属配線から極性溶媒に移動したときの領域の損傷を抑制するように、金属配線の配置を決定するステップとを含むものとする。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の特性を保持或いは高めると共に小型化を図る。

【解決手段】 主面および前記主面とは反対側の裏面を有し、第1辺を含む平面形状が矩形状の半導体基板と、前記主面上に形成された複数のボンディングパッドと、前記主面上に形成された内部回路形成部と、前記第1辺と前記内部回路形成部との間に配置されており、前記内部回路形成部に電位を供給する内部回路用電源配線と、前記第1辺と前記内部回路用電源配線との間に配置されており、前記複数のボンディングパッドと電気的に接続され、トランジスタを備えた複数のセルと、前記複数のセル上に配置され、前記複数のセルに電位を供給するセル用電源配線と、を有し、前記複数のセルは、外部からの入出力信号を送受信する回路を含む入出力セルを有し、前記複数のボンディングパッドのそれぞれは、前記入出力セルと平面的に重なるように配置されている。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】MIM容量の搭載数を変化させた評価を、効率良く行うことができる半導体装置及びそのレイアウト方法。

【解決手段】本発明に係る半導体装置は、下層電極107と、上層電極109と、両電極間に形成された容量絶縁膜108を有するMIM容量MC1と、下層電極107に接続され、下層電極107の主面の法線方向上向きに延設された第1のビアホールVHcと、上層電極109に接続され、上層電極109の主面の法線方向上向きに延設された第2のビアホールVHbと、下層電極107よりも下側に形成された複数の下層配線102と、を備え、上層電極109の主面の法線方向から見た場合、第1及び第2のビアホールVHc、VHbが下層配線102と重なって形成されているものである。

(もっと読む)

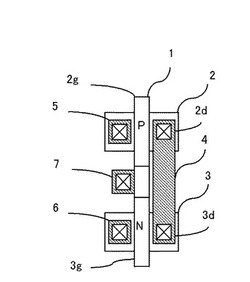

スタンダードセルおよび半導体装置

【課題】回路動作に必要な配線を形成するための領域が広く、回路の高速動作が可能なスタンダードセルを提供する。

【解決手段】第1のMOS素子および第2のMOS素子に信号を供給するための信号線が、電源配線および接地配線の2つの配線と平行に設けられ、これら2つの配線に挟まれ、かつ、第1の導電型MOS素子および第2の導電型MOS素子のそれぞれから等しい距離に配置されている構成である。

(もっと読む)

81 - 100 / 366

[ Back to top ]