Fターム[5F064EE32]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713)

Fターム[5F064EE32]の下位に属するFターム

Fターム[5F064EE32]に分類される特許

121 - 140 / 366

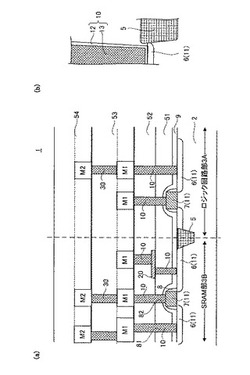

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

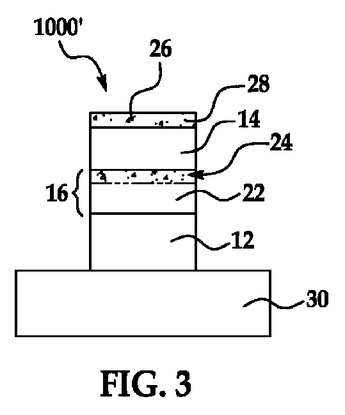

グリッドプレートを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(200)は、集積回路の第1のパターニングされた金属層に形成された分配グリッド(226)と、分配グリッドに接続され、分配グリッドから離れる方に第1の方向に沿って延在する第1の縦方向導電性フィラメント(202)とを含む。第2の縦方向導電性フィラメント(203)は、分配グリッドに接続され、反対方向に延在する。第1のグリッドプレート(225)および第2のグリッドプレート(224)は、第1のパターニングされた金属層の上および下に形成される。グリッドプレートは、第1のおよび第2の縦方向導電性フィラメントを包囲する。分配グリッド、第1の縦方向導電性フィラメント、および第2の縦方向導電性フィラメントは、キャパシタの第1のノードに接続され、かつ第1のノードの一部分を形成し、第1のグリッドプレートおよび第2のグリッドプレートは、キャパシタの第2のノードに接続され、かつ第2のノードの一部分を形成する。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造安定性に優れ、接触抵抗の低減を図ることができる半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、上層配線12と、下層配線11と、上層配線12および下層配線11間に配置された絶縁層22〜24と、絶縁層22〜24中に形成されて上層配線12および下層配線11を接続する接続部13と、絶縁層24中に配置されて、接続部13に接続される導電層を有する素子14とを有する。接続部13は、下層配線11上および素子14の前記導電層の端部上にわたって配置され、接続部13は、下層配線11上面、素子14の導電層の端部の上面および側面に接触している。

(もっと読む)

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】上層配線の幅によらずにコンタクトプラグの底面がアンカー構造となり、下層配線との接続抵抗を低減できる半導体装置とその製造方法を提供する。

【解決手段】基板に下層配線W1となる第1導電層を形成し、絶縁膜を形成し、上層配線用溝とこれに連通するようにコンタクトホールCHを形成する。次に、コンタクトホール及び上層配線用溝の内壁面を被覆してバリアメタル層を形成し、その上層にコンタクトホール及び上層配線用溝に埋め込んで第2導電層を形成する。ここで、上層配線用溝及びコンタクトホールを形成する工程において、上層配線W2と下層配線W1の交差する領域に、上層配線にスリットSL1,SL2または切り欠きを設けて幅が狭くなった部分NPが設けられるように上層配線用溝を形成し、この幅が狭くなった部分NPにおいてコンタクトホールCHを形成する。

(もっと読む)

電気的に作動するデバイス及びそのデバイスにおけるドーパントの形成を制御する方法

電気的に作動するデバイスが、第1の電極、第2の電極並びに当該第1及び第2の電極間に堆積させた活性領域を備えている。当該デバイスは、i)第1の電極と活性領域との界面、又はii)第2の電極と活性領域との界面、又はiii)活性領域と第1及び第2の電極のそれぞれとの各界面で局在化された、少なくとも1つのドーパント導入剤又はドーパントをさらに含む。  (もっと読む)

(もっと読む)

レイアウト評価装置、レイアウト評価プログラム、ダミールール生成装置及びダミールール生成プログラム

【課題】回路レイアウト毎の平坦性評価を高速に実行し、ダミーフィルを支援すること。

【解決手段】レイアウトパターンにCMPを行なった際の高さばらつきが指定された上限となる配線密度、配線周囲長、密度差最大値の範囲をクリティカル領域として求める。そして、入力されたレイアウトパターンをメッシュ分割して各メッシュの配線密度、配線周囲長、密度差最大値をメッシュデータとして算出し、各メッシュのメッシュデータがクリティカル領域にあるか否かを示すクリティカリティマップと、パターン全体の高さばらつきの予測値とを算出する。

(もっと読む)

半導体装置

【課題】面積の増加なしに、印加電圧の揺らぎの許容範囲を広くする。

【解決手段】半導体装置200は、電気ヒューズ100と、電気ヒューズ100に電圧を印加するための第1の大面積配線116および第2の大面積配線126とを含む。電気ヒューズ100は、上層ヒューズ配線112と、下層ヒューズ配線122と、上層ヒューズ配線112および下層ヒューズ配線122とを接続するビア130と、から構成されるヒューズユニット102と、上層ヒューズ配線112と第1の大面積配線116とを接続するとともに、屈曲したパターンを有する上層引出配線114と、下層ヒューズ配線122と第2の大面積配線126とを接続するとともに、屈曲したパターンを有する下層引出配線124とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】繋ぎ露光において、マスクパターンの一端部を幅広に形成したマスクを使用しなくても、マスクの相対的な位置ずれに伴う配線抵抗の増大や配線信頼性の低下などの電気的な特性劣化を抑制する。

【解決手段】本発明の半導体装置は、半導体基板上で隣り合う第1の露光領域及び第2の露光領域のうち、第1の露光領域に第1の露光マスクを用いて形成された第1配線パターン101と、第1配線パターン101と繋ぎ合わせるための配線パターンとして、第1配線パターン101と同層でかつ第2の露光領域に第2の露光マスクを用いて形成された第2配線パターン102と、第1配線パターン101と第2配線パターン102との繋ぎ合わせ部分に形成されたビア103,104と、ビア103,104の間に形成された繋ぎパターン105とを備える。

(もっと読む)

半導体集積回路

【課題】配線効率を悪くすることなく効率よくノイズを除去可能な半導体集積回路を提供する。

【解決手段】スタンダードセル10に論理回路領域10aと容量領域10bとを具備させ、同一の配線層に属する1本の電源配線22及び2本の接地配線20,21(または2本の電源配線及び1本の接地配線)をスタンダードセル10に接続し、容量領域10bにおいて、MOS容量17を同一の配線層の電源配線22と接地配線21との間に接続する。

(もっと読む)

集積回路設計中の製造の影響の高速シミュレーションを行なうための装置、方法及びコンピュータ・プログラム

【課題】 設計段階中の集積回路の電気性能への製造プロセスの影響のシミュレーションを行なうための方法、装置及びコンピュータ・プログラムを提供すること。

【解決手段】 集積回路の設計を生成し、集積回路の設計を生成しながら、簡単化されたモデルを用いて集積回路の製造中に用いられることになる処理ステップから結果として生じる集積回路の少なくとも1つの物理的特性を予測し、簡単化されたモデルは、物理的特性をモデル化するために用いられる包括的シミュレーション・プログラムを用いて設計生成作業の前に実行されたシミュレーションから得られ、予測された物理的特性を用いて集積回路の性能を予測し、性能の予測に基づいて集積回路の設計を調整することによって、集積回路の製造中の化学機械研磨(CMP)ステップの影響をシミュレートするための高速かつ正確なモデルを方法、装置及びコンピュータ・プログラムが提供する。

(もっと読む)

半導体装置

【課題】複数の半導体チップが同一パッケージに積層された半導体装置に関し、複数の半導体チップのいずれかで生成される電圧を、他の半導体チップに電源電圧として供給し、安定して動作できる技術を提供する。

【解決手段】主なものの1つの例として、2つのチップを積層して、パッドA,BおよびCをそれぞれのチップの並んだ辺に配置し、それらのパッドをそれぞれ金属線wireA,BおよびCで共通に接続する。もう1つの例は、パッドA,BおよびCが配置された辺とは異なる辺に沿ってパッドHおよびパッドJを配置し、さらに金属線wireHJによりチップ間ボンディング接続する。

(もっと読む)

半導体回路装置及び半導体回路装置製造方法

【課題】半導体回路装置のレイアウトに対する少ない調整により、当該半導体回路装置に生じた伝搬遅延時間の設計値からのずれを調整することのできる半導体回路装置を提供する。

【解決手段】CMPによる配線構造のばらつきを抑えるために設けられる複数のダミーメタルC1〜C5それぞれが、層間容量を有するようにダミーメタルの直上・直下に予めメタル領域・ポリシリコン領域を配置する。伝播遅延時間の調整が必要な配線には、当該配線が配置されるメタル層のマスクパターンのみを変更して、ダミーメタルC1〜C5を当該配線に接続して配線の容量を増加させることにより伝搬遅延時間を調整する。

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含む電気ヒューズ100であって、切断状態において、電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、上層配線110および下層配線120の一方と同層に上層配線110および下層配線120の一方の側方に形成されるとともに、上層配線110および下層配線120と電気的に接続された熱拡散用上層配線152aを含む熱拡散部150aとを含む。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置のロジック領域に冗長救済を行う構成を提供することを目的とする。

【解決手段】本発明の1つの実施の形態は、ロジック領域2を有する半導体装置1である。そして、当該半導体装置1は、ロジック領域2内に設けられる同一の構成を有する複数の基本セル21と、複数の基本セル21と同一の構成を有する冗長セル22と、複数の基本セル21及び冗長セル22のそれぞれに入力される信号を切り替える入力セレクタ23と、基本セル21及び冗長セル22のそれぞれから出力される信号を切り替える出力セレクタ24とを備えている。さらに、当該半導体装置1は、入力セレクタ23及び出力セレクタ24のうち少なくとも一方を切り替えて、冗長セル22を機能させ複数の基本セル21のうち故障したセルを救済する。

(もっと読む)

半導体装置及びその製造方法

【課題】追加工程なくフューズ下に配線等を配置可能な半導体装置及びその製造方法を提供する。

【解決手段】この半導体装置は、絶縁層に設けられた複数の第1キャパシタ孔52と、第1キャパシタ孔52に形成された容量素子Cと、容量素子Cと結合するトランジスタTrとからなるDRAMセルと、絶縁層に設けられた複数の第2キャパシタ孔40と、第2キャパシタ孔40の間に形成されるフューズ素子(31、51)と、を備えている。

(もっと読む)

膜厚予測方法、レイアウト設計方法、露光用マスクのマスクパターン設計方法、及び、半導体集積回路の作製方法

【課題】回路パターンの上に形成される薄膜の膜厚をより正確に予測し得る膜厚予測方法を提供する。

【解決手段】膜厚予測方法にあっては、第2の被処理層の断面形状に関する第1の実測データベース、回路パターンの周辺長と第2の被処理層の厚さとの関係に関する第2の実測データベース、第2の被処理層の平坦化レートに関する第3の実測データベース、第2の被処理層の基準膜厚Tblkを予め求めておき、基板の上に形成すべき第1の被処理層を所定の大きさの碁盤目状のメッシュに区切り、各メッシュ(i,j)におけるパターン面積率αij、回路パターンの周辺長Lij、第2の被処理層の初期厚さT2_INI_ij、基準膜厚Tblk、第1の実測データベース、第2の実測データベース及び第3の実測データベースに基づき、第2の被処理層の初期膜厚予測値Prij及び第2の被処理層の平坦化量Hijを求め、第2の被処理層を平坦化した後の第2の被処理層の膜厚を予測する。

(もっと読む)

半導体集積回路及び半導体集積回路のレイアウト方法

【課題】上地層における信号配線を妨げることなく電源配線パターンの強化を行うことができる、半導体集積回路及び半導体集積回路のレイアウト方法を提供する。

【解決手段】論理素子が設けられた下地層と、前記下地層上に設けられた上地層とを備える半導体集積回路のレイアウト方法において、前記上地層に複数本に延びる電源配線をレイアウトし、電源配線データを生成するステップと、前記下地層に前記論理素子をレイアウトし、論理素子データを生成するステップと、前記電源配線データ及び前記論理素子データに基づいて、前記下地層に、導電性である電源強化用パターンをレイアウトし、電源強化用パターンデータを生成するステップとを具備し、前記電源強化用パターンデータを生成するステップは、前記電源強化用パターンを、前記下地層における前記論理素子がレイアウトされていない領域に、前記複数本に延びる電源配線パターン同士が接続されるようにレイアウトするステップを備えている。

(もっと読む)

MOSトランジスタ、CMOS及びこれを用いたモータ駆動用半導体集積回路装置

【課題】本発明は、製造工程の大きな変更もなく、1枚のマスクの変更のみで駆動時の出力波形の立ち上がりの時間的変化率を緩やかにできるMOSトランジスタを提供することを目的とする。

【解決手段】半導体基板上80に所定のゲート幅Wを有して延在する複数のゲート10が略平行に配置され、該ゲートの両側にソース20とドレイン30が交互に配置された複数のトランジスタセルを含むMOSトランジスタ100、100aであって、

前記ゲート10の両端部11、12と平面視的に重なり、前記ゲート10の両端部11、12から同電位の供給が可能に配置されたゲート配線層70を有し、

該ゲート配線層70と前記ゲート10の端部とを電気的に接続するゲートコンタクト40が、前記ゲート10の端部11、12の片側のみに設けられたトランジスタセルを含むことを特徴とする。

(もっと読む)

半導体装置、セルライブラリおよび半導体集積回路の設計方法

【課題】回路設計に要する期間を短縮することが可能な機能セルとその機能セルを含む半導体装置およびその機能セルを用いた半導体回路設計方法を提供する。

【解決手段】半導体装置は、同一の論理回路機能を実現し、互いに電気的特性の異なる第1および第2の機能セル3a、3bを備える。第1の機能セル3aは第1の外部接続配線を含む。第2の機能セル3bは第2の外部接続配線を含む。第1の機能セル3aの外周の形状は、第2の機能セル3bの外周の形状とほぼ同一である。第1の外部接続配線の第1の機能セル3a平面内における位置は、第2の外部接続配線の第2の機能セル3b平面内における位置とほぼ同一である。

(もっと読む)

121 - 140 / 366

[ Back to top ]