Fターム[5F083JA31]の内容

Fターム[5F083JA31]の下位に属するFターム

Si (497)

シリサイド (3,215)

Al、Al系合金 (2,881)

Cu、Cu系合金 (2,136)

白金族元素、Au、及び、その合金 (2,740)

高融点金属(W、Mo、Ta、Ti、Ni)及びその合金 (5,337)

金属窒化物 (3,610)

酸化物導電体 (2,345)

化合物半導体(III−V族,II−VI族) (27)

ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA31]に分類される特許

141 - 152 / 152

半導体装置、及びそれらの作製方法

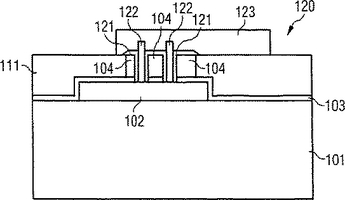

【課題】 本発明では、工程、装置を複雑化することなく、要求される特性を有する薄膜トランジスタを作製することを目的とする。また、薄膜トランジスタの特性を精密に自由に制御することで、高い信頼性や優れた電気特性を有する半導体装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】 本発明は、薄膜トランジスタにおいて、ゲート電極層で覆われている半導体層のソース領域側かドレイン領域側の一方に、低濃度不純物領域を作製する。低濃度不純物領域は、ゲート電極層をマスクとして、半導体層表面に対し、斜めにドーピングすることによって形成される。よって、薄膜トランジスタの微細な特性の制御を行うことができる。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

ドーピング装置

【課題】 本発明は、大量生産上、多面取りが可能な大面積基板を用いて不純物元素を均一にドーピングする装置を備えた半導体装置の製造装置を提供する。

【解決手段】 本発明は、イオン流の断面を線状もしくは長方形とし、かつ、イオン流に対し大面積基板を所定の傾斜角度θだけ傾斜させた状態に保ったまま、大面積基板をイオン流の長尺方向と垂直な方向に移動させることを特徴の一つとしている。本発明において、イオンビームの入射角は、傾斜角度θを変更することによって調節する。水平面に対し大面積基板を傾斜状態とすることで、イオン流の長尺方向の幅を基板の一辺の長さよりも短くすることができる。

(もっと読む)

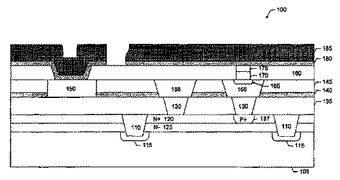

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

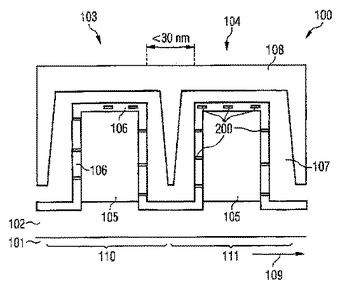

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

高密度データ記憶のための高度に分解されたドメインを書き込み及び読み取りする方法

本発明による方法は、一実施形態において、相変化材料を含む媒体に適用して、相変化材料の分解される部分を、バルク材料の抵抗とは異なる抵抗を有するように変更することができる。この方法を適用することにより、分解される部分より実質的に曲率半径が大きいチップを使用することができる。実質的に非等方性の柱状材料は、チップと媒体との間に付与される電流を収束して、前記部分の幅を曲率半径より狭くすることができる。このように高度に分解された部分が媒体にビットを形成する。本発明の他の目的、態様及び効果は、添付図面、明細書及び特許請求の範囲を検討することから得ることができる。この説明は、本発明の完全な説明を意図しておらず、又、本発明の範囲を限定するものではない。  (もっと読む)

(もっと読む)

ポリマーメモリ装置の金属窒化物電極及び金属酸化物電極内への電子トラップ生成

本発明の一実施形態は、ポリマー強誘電体メモリ装置のポリマー強誘電体層に引き起こされるダメージを、金属電極とポリマー強誘電体層との間の絶縁性の金属窒化物及び/又は金属酸化物層に過剰正孔を生成することによって低減する。交流バイアスの下で金属電極から注入される電子はポリマー強誘電体層にダメージを与えるものであるが、金属窒化物及び/又は金属酸化物における過剰正孔がこのような電子をトラップする。 (もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

141 - 152 / 152

[ Back to top ]