Fターム[5F083JA31]の内容

Fターム[5F083JA31]の下位に属するFターム

Si (497)

シリサイド (3,215)

Al、Al系合金 (2,881)

Cu、Cu系合金 (2,136)

白金族元素、Au、及び、その合金 (2,740)

高融点金属(W、Mo、Ta、Ti、Ni)及びその合金 (5,337)

金属窒化物 (3,610)

酸化物導電体 (2,345)

化合物半導体(III−V族,II−VI族) (27)

ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA31]に分類される特許

121 - 140 / 152

半導体装置、及び半導体装置の作製方法

【課題】より高機能、高信頼性の半導体装置、及びそのような半導体装置を工程、装置を複雑化することなく低コストで、歩留まりよく作製できる技術を提供することを目的とする。

【解決手段】第1の導電層及び第2の導電層の少なくとも一方をインジウム、錫、鉛、ビスマス、カルシウム、マンガン、及び亜鉛のうち一種又は複数種を含んで形成する、又は第1の導電層及び第2の導電層の少なくとも一方と、有機化合物層との界面において酸化処理を行う。第1の基板上に剥離層を介して設けられる第1の導電層、有機化合物層、及び第2の導電層は、剥離層より第1の基板より剥離され第2の基板に転置することができる。

(もっと読む)

金属−絶縁体転移膜の抵抗体を含む半導体メモリ素子

【課題】低い漏れ電流及び高い信頼性、例えば長いリテンション時間及び短いリフレッシュ時間を有する半導体メモリ素子を提供する。

【解決手段】スイッチング素子及びキャパシタを備える半導体メモリ素子であり、該スイッチング素子のソースは、金属−絶縁体転移膜の抵抗体の一端に連結され、キャパシタの一つの電極は、金属−絶縁体転移膜の抵抗体の他端に連結される。金属−絶縁体転移膜の抵抗体は、両端に印加された電圧に応じて絶縁体と導電体との間で転移が可能である。

(もっと読む)

記憶装置及び半導体装置

【課題】書込みの信頼性が高く、安価な記憶装置及び半導体装置を提供する。また、製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶素子を有する記憶装置及び半導体装置を提供する。

【解決手段】記憶素子は、第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形成され、且つ、電子と正孔の再結合エネルギーにより励起状態となりうる光増感酸化還元剤及び光増感酸化還元剤により反応しうる基質を有する有機化合物を含む層とを有する。

(もっと読む)

イオン伝導層を備える不揮発性半導体メモリ装置とその製造及び動作方法

【課題】イオン伝導層を備える不揮発性半導体メモリ装置とその製造及び動作方法を提供する。

【解決手段】基板と、前記基板に形成されたスイッチング素子と、スイッチング素子に連結されたストレージノードと、を備える不揮発性メモリ装置において、ストレージノードは、スイッチング素子に連結され、イオンソースとして使われる下部電極と、下部電極上に形成され、その一部は下部電極と離隔されたデータ保存層と、下部電極から離隔された前記データ保存層の部分に側面が連結され、下部電極と離隔されている側部電極と、データ保存層上に形成された上部電極と、を備えることを特徴とする不揮発性メモリ装置とその製造及び動作方法。

(もっと読む)

金属酸化物素子及びその製造方法

【課題】より安定に状態の保持が得られるなど、金属酸化物から構成された材料を用いて安定した動作が得られる金属酸化物素子を提供する。

【解決手段】単結晶シリコンからなる基板101の上に絶縁層102,共通に設けられた下部電極層103,BiとTiとOとから構成された膜厚30〜200nm程度の複数の金属酸化物層104,金属酸化物層104毎に設けられた上部電極105を備える。また、隣り合う酸化物層104の間が、五酸化タンタルからなる絶縁分離層106により素子分離されている。

(もっと読む)

半導体装置およびその作製方法

【課題】有機層の上に電極を形成することは形成時の温度によっては有機層への影響があるため温度に制限があり、希望通りの電極を形成することができず素子の微細化を阻害している問題があった。

【解決手段】記憶素子の二端子として、2つの電極を同じ層に配置し、それらの間に有機化合物を含む層を設けた有機記憶素子の構造を提供する。2つの電極の間隔を狭めることによって、低電圧での書き込みを行うことが可能である。また、記憶素子の構造が簡素化され、記憶素子の占有面積を縮小することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体膜のチャネル領域の端部におけるゲート絶縁膜の段切れや薄膜化により生じる半導体膜とゲート電極とのショートやリーク電流を抑制する半導体装置および当該半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に連続して設けられた半導体膜と、半導体膜の上方にゲート絶縁膜を介して設けられた導電膜と、導電膜と重ならない半導体膜に形成されたソース領域及びドレイン領域と、導電膜の下方に位置する半導体膜であってソース領域とドレイン領域の間に形成されたチャネル領域とを有する複数の薄膜トランジスタと、導電膜と重ならない半導体膜であってソース領域及びドレイン領域と隣接して設けられた不純物領域とを有し、導電膜をチャネル領域及びチャネル領域に隣接する半導体膜上に設ける構成とする。

(もっと読む)

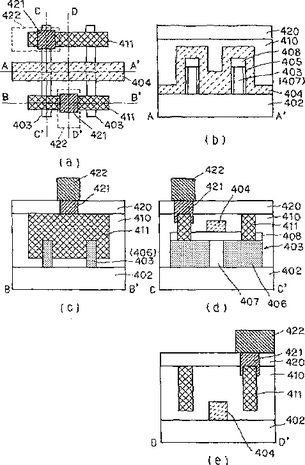

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

強誘電性薄膜を形成するための方法、該方法の使用、及び強誘電性オリゴマーメモリ材料を有するメモリ

フッ化ビニリデンオリゴマー又はフッ化ビニリデンコオリゴマーの強誘電性薄膜を形成するための方法において、オリゴマー材料が、真空室内で蒸着され且つ基板上に薄膜として堆積され、基板は、堆積されたVDFオリゴマー又はコオリゴマー薄膜のプロセスパラメータ及び物理特性によって決定される範囲の温度に冷却される。強誘電性メモリセル又は強誘電性メモリデバイスを製造するための本発明の方法の適用において、強誘電性メモリ材料は、電極構造間に配置されるVDFオリゴマー又はVDFコオリゴマーの薄膜の形態で設けられる。この方法で製造される強誘電性メモリセル又は強誘電性メモリデバイスは、薄膜が、少なくとも1つの電極構造上に又は第1電極構造と第2電極構造との間に設けられるように、少なくとも1つの第1電極構造及び第2電極構造上に設けられたVDFオリゴマー又はVDFコオリゴマーの薄膜の形態のメモリ材料を有する。  (もっと読む)

(もっと読む)

ゲート電極積層およびゲート電極積層を用いる方法

【課題】エッチングの容易なポリシリコン−メタル積層で構成されるゲート電極構造を提供する。

【解決手段】少なくとも1層のポリシリコン3と少なくとも1層のポリSi1−xGex材料の層4とを有するゲートコンダクタを備える半導体デバイスの基板上のゲート電極積層構造であり、ポリシリコン3とポリSi1−xGex材料の層4のエッチングにより、終点検出が可能であるため、上記構造を効果的にエッチングすることができる。

(もっと読む)

半導体集積回路用キャパシタ

【課題】 層間絶縁膜に埋め込まれた導電プラグ上にキャパシタを形成する場合、その導電プラグ上にPZTなどを成膜する際の成膜温度を抑える必要性がなく、且つ、PZTの製造時に生じる酸素の下部電極への内向拡散を抑制することを可能にしようとする。

【解決手段】 層間絶縁膜1に埋め込まれた導電性プラグ2の頂面を含む領域にSiO2 、SiN、Al2 O3 から選択されたアモルファスの第1層3A、第1層3A上に形成されたTiAlN或いはTi/TiAlNからなる第2層3B、Ir或いはIrO2 からなる第3層3Cで構成された下部電極3と、下部電極3上に順に形成された誘電体層4及び上部電極5とを備える。

(もっと読む)

分子電子素子のための複合有機分子

電子素子において導電経路として有用な複合分子が提供される。この複合分子は、電子流に方向付けを提供するために、少なくとも一のp/n接合を含み、そして素子における集合の間にこの分子に自己配向を与える一末端ワニ口クリップ基を含み、この分子の構造を非対称にする。この複合分子は、ダイオード、分子スイッチ、トランジスタにおいて、およびメモリー素子の製造において使用され得る。 (もっと読む)

半導体装置

【課題】 強誘電体膜と強磁性体膜との2つの層を積層することなく、かつ強磁性及び強誘電性を損なうことのない構造を有する半導体装置を提供する。

【解決手段】 半導体からなる表層部を含む基板1の該表層部内のチャネル領域2の両側に、ソース領域3及びドレイン領域4が形成されている。チャネル領域の上にゲート絶縁膜7が形成されている。ゲート絶縁膜の上に被制御膜9が形成されている。被制御膜は、強誘電性を示すとともに、強磁性またはフェリ磁性をも示す。被制御膜の上にゲート電極10が形成されている。被制御膜の磁化の向きを変化させる磁化制御構造が設けられている。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】高誘電体膜を介するリーク電流の低減が可能な半導体装置を提供する。

【解決手段】単結晶のシリコン領域6と、シリコン領域6上に設けられシリコンとゲルマニウムの少なくとも1つの元素を含む多結晶又はアモルファスの半導体膜7と、半導体膜7上に設けられた高誘電体膜8と、高誘電体膜8上に設けられた電極12を有する。

(もっと読む)

有機薄膜の形成方法、強誘電体膜、圧電体膜、強誘電体キャパシタの製造方法、圧電素子の製造方法、強誘電体メモリ、圧電アクチュエータ、インクジェット式記録ヘッド、インクジェットプリンタ、および電子機器。

【課題】 より簡易な工程で形成できる有機系材料からなる有機薄膜の形成方法を提供する。

【解決手段】 本発明の有機薄膜20の形成方法は、

(a)基体10の上に接着用溶液を塗布すること、

(b)前記接着用溶液が塗布された前記基体10の上に、配向が制御されたシート状の有機系材料膜20aを接着すること、

(c)前記有機系材料膜20aの膜厚を制御すること、を含む。

(もっと読む)

ハイブリッドマルチビット不揮発性メモリ素子及びその動作方法

【課題】ハイブリッドマルチビット不揮発性メモリ素子を提供する。

【解決手段】第1方式でデータを保存できる第1ストレージノードを備えている第1メモリ部と、第1メモリ部とは異なる第2方式でデータを保存できる第2ストレージノードを備えている第2メモリ部とを備える不揮発性メモリ素子である。第1メモリ部及び第2メモリ部は、ソース及びドレインを共有して2ビット以上のマルチビット動作が可能である。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体膜上にシリコン含有の電極を有し、長期信頼性の優れたMISFET、MISキャパシタで成る高性能な半導体装置の製造を可能にする。

【解決手段】 半導体基板上に高誘電体膜を形成する工程、この高誘電体膜に対して酸化性雰囲気中の第1の熱処理(第1のPDA)を施す工程、第1のPDA後に、前記高誘電体膜表面に窒化シリコン層を形成する工程、前記窒化シリコン層により被覆された高誘電体膜および窒化シリコン層に対して第2の熱処理(第2のPDA)を施す工程、窒化シリコン層上にシリコン含有の半導体膜もしくは導電体膜を形成する工程、を通して高誘電体ゲート絶縁膜およびゲート電極等を形成することで、長期信頼性の優れた高性能のMISFET等が実現できる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】 半導体素子上に、金属酸化物を含む薄膜が形成されてなる半導体デバイスを形成する際に、半導体素子に熱損傷を与えない程度の低温にて形成可能な半導体デバイスを提供する。

【解決手段】

半導体デバイスは、半導体素子上に、金属酸化物を含む薄膜(106)が形成されてなる半導体デバイスであって、薄膜(106)は、金属酸化物よりなる複数の結晶粒子(106a)の集合体であり、複数の結晶粒子(106a)の各々は、表面の一部において、隣接する結晶粒子と結合している。

(もっと読む)

半導体装置及びその製造方法

【課題】 成膜中に低誘電率界面層を生成させず、かつ熱処理後も低誘電率界面層の生成を抑制でき、ゲート絶縁膜としての High-k膜を有効利用する。

【解決手段】 Si基板10上にゲート絶縁膜12を形成した後にゲート電極13を形成する工程を含む半導体装置の製造方法であって、ゲート絶縁膜12として、Zr,Hf,Ti,及びランタノイド金属のうち少なくとも一つを含む酸化膜を、500℃以上800℃以下の温度領域で、且つ酸素分圧が1×10-4Pa以下の雰囲気下で成膜する。

(もっと読む)

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

121 - 140 / 152

[ Back to top ]