Fターム[5F083JA31]の内容

Fターム[5F083JA31]の下位に属するFターム

Si (497)

シリサイド (3,215)

Al、Al系合金 (2,881)

Cu、Cu系合金 (2,136)

白金族元素、Au、及び、その合金 (2,740)

高融点金属(W、Mo、Ta、Ti、Ni)及びその合金 (5,337)

金属窒化物 (3,610)

酸化物導電体 (2,345)

化合物半導体(III−V族,II−VI族) (27)

ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA31]に分類される特許

41 - 60 / 152

金属酸化物抵抗率スイッチング層と共に使用する下部電極

金属酸化物抵抗率スイッチング層と共に使用する下部電極

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

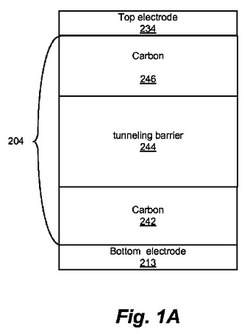

炭素/トンネル障壁/炭素・ダイオード

炭素/トンネル障壁/炭素・ダイオード及び炭素/トンネル障壁/炭素・ダイオードの形成方法を開示する。炭素/トンネル障壁/炭素はメモリアレイ内でステアリング素子として用いられてもよい。メモリアレイ内の各メモリセルは可逆的抵抗性スイッチング素子、及びステアリング素子として炭素/トンネル障壁/炭素・ダイオードを含んでいてもよい。トンネル障壁は半導体又は絶縁体を含んでいてもよい。従って、ダイオードは炭素/半導体/炭素・ダイオードであってもよい。ダイオード内の半導体は真性であってもよいし、ドープされていてもよい。ダイオードが平衡状態にある場合は、半導体が空乏化されることがある。例えば、空乏領域が半導体領域の一端から他端まで延びるように、半導体が低濃度にドープされてもよい。ダイオードは炭素/絶縁体/炭素・ダイオードであってもよい。 (もっと読む)

エレクトロルミネッセンス配合物

発明は、小分子有機機能性材料を含む乳濁液及び分散液、それらの調製のため方法、小分子有機機能性材料と、任意にさらなる有機機能性材料とを含むエレクトロニクス素子及びエレクトロニクス素子の調製のためのそれらの使用に関する。 (もっと読む)

可変抵抗メモリ装置の製造方法及び可変抵抗メモリ装置

【課題】相変化物質膜を有する可変抵抗メモリ装置の加熱電極の形成方法とこれを利用する可変抵抗メモリ装置を提供する。

【解決手段】可変抵抗メモリ装置の製造方法は、加熱電極を形成し、加熱電極上に可変抵抗の物質膜を形成し、そして、可変抵抗の物質膜上に上部電極を形成する。加熱電極はチタニウムより原子の半径が大きい金属窒化物を含み、プラズマを利用しない熱化学蒸着(thermal CVD)法で形成される。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

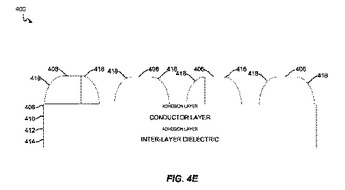

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

誘電体膜をパッシベーションする方法

塩素、臭素又はヨウ素と反応しやすい誘電体材料にフッ素を含むパッシベーション層を堆積する方法が本明細書に開示される。パッシベーション層は、反応しやすい誘電体層を保護することができ、それにより、パッシベーション層に塩素、臭素又はヨウ素を含む前駆体を用いて堆積が可能となる。 (もっと読む)

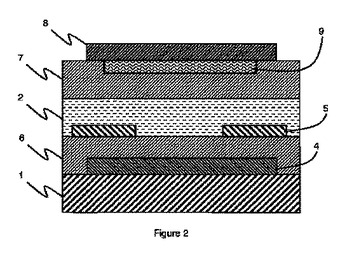

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

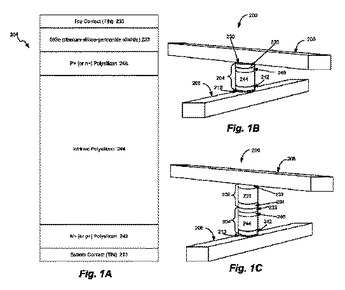

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】消費電力を低減させ且つ誤動作を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】可変抵抗層63は、炭素C、及び元素群Aから選ばれる少なくともいずれか1種類以上の元素を含む第1化合物631と、化合物群G2から選ばれる少なくともいずれか1種類以上の第2化合物632とを含む混合体にて構成されている。可変抵抗層63中での第1化合物631の濃度は、30vol.%以上であり且つ70vol.%以下である。元素群G1は、水素、ボロン、窒素、シリコン、及びチタンを含む。化合物群G2は、酸化シリコン、酸窒化シリコン、窒化シリコン、窒化炭素、窒化ホウ素、窒化アルミニウム、アルミニウム酸化物、炭化珪素を含む。

(もっと読む)

DRAMセル

【課題】DRAMセルの密度を向上させ、製造工程を簡素化し、リフレッシュレートを下げることができるDRAMセルを提供する。

【解決手段】DRAMセルは、半導体材料からなり、主表面102を有する基板100と、主表面102に形成されたトランジスタ120と、トランジスタ120の上方に設けた金属層に形成した磁器コンデンサ140とを備える。磁器コンデンサ140は、第1の磁性層142と、第1の磁性層142上に形成した誘電体層144と、誘電体層144上に形成した第2の磁性層146とを有する。誘電体層144が非導電性材料からなり、第1の磁性層142及び第2の磁性層146がCoNiFe合金からなる。

(もっと読む)

炭素ナノチューブを利用した相変化メモリ及びその製造方法

【課題】相変化メモリにおいて、相変化物質と下部電極との接触面積を画期的に減らして、低電力で動作可能であり、かつ、集積度をさらに向上させることができる炭素ナノチューブを利用した相変化メモリ及びその製造方法を提供すること。

【解決手段】外部電流を供給する電流源電極と、少なくとも2つの異なる状態を有する相変化物質層と、電流源電極と相変化物質層との間に複数配列した炭素ナノチューブ電極と、炭素ナノチューブ電極の外側に形成される絶縁体と、炭素ナノチューブ電極と相変化物質層との間に位置し、炭素ナノチューブ電極と接触する熱生成抵抗層とを備えることを特徴とする炭素ナノチューブを利用した相変化メモリ。

(もっと読む)

可逆抵抗切替素子の書き込み

可逆抵抗切替素子を使用する記憶システムと、その記憶システムを動作させる方法が記載される。ここでは、メモリセルが有する様々な抵抗を考慮して、書き込み条件を変更する技術が開示される。これらの技術は、少数回の試行によってメモリセルへの書き込みが可能であり、時間及び/又は電力を節約することができる。また、電流/電力の最大時の消費量を抑制しつつ、高い書き込み帯域幅を実現するための技術が開示される。一実施形態では、電流/電力の最大時の消費量を削減するべく、複数のメモリセルに同時に書き込みを行うためのページマッピング方式が提供される。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】隣接セルとの容量を低減し、カップリング比を向上させる。

【解決手段】半導体記憶装置は、半導体基板101と、前記半導体基板上に所定間隔を空けて設けられた複数の第1の絶縁膜103と、前記第1の絶縁膜間にビット線方向に沿って設けられた素子分離領域102と、前記第1の絶縁膜上に設けられた第1の電荷蓄積膜104a、前記第1の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第1の電荷蓄積膜より狭い第2の電荷蓄積膜104b、及び前記第2の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第2の電荷蓄積膜より広い第3の電荷蓄積膜104cを有する電荷蓄積層104と、前記第2の電荷蓄積膜と前記素子分離領域との間に設けられた第2の絶縁膜107と、前記電荷蓄積層上及び前記素子分離領域上に前記第2の方向に沿って設けられた第3の絶縁膜105と、前記第3の絶縁膜上に設けられた制御ゲート電極106と、を備える。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

41 - 60 / 152

[ Back to top ]