Fターム[5F083JA31]の内容

Fターム[5F083JA31]の下位に属するFターム

Si (497)

シリサイド (3,215)

Al、Al系合金 (2,881)

Cu、Cu系合金 (2,136)

白金族元素、Au、及び、その合金 (2,740)

高融点金属(W、Mo、Ta、Ti、Ni)及びその合金 (5,337)

金属窒化物 (3,610)

酸化物導電体 (2,345)

化合物半導体(III−V族,II−VI族) (27)

ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA31]に分類される特許

21 - 40 / 152

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

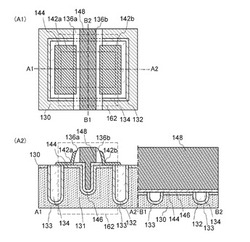

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

不揮発性抵抗変化素子

【課題】電極との間で金属の出し入れが行われることで可逆的に抵抗が変化される抵抗変化層の絶縁性の劣化を抑制する。

【解決手段】抵抗変化層2は半導体元素を有し、第2電極4の金属元素が出し入れされることで可逆的に抵抗変化が可能で、誘電体層3は、第2電極4と抵抗変化層2との間に挿入され、抵抗変化層2よりも第2電極4の金属元素の拡散係数が小さい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイに用いられる配線の抵抗を低減することができる半導体記憶装置の製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置の製造方法は、第1配線層を積層する工程と、第1配線層の上方にメモリセル層を積層する工程と、メモリセル層の上方に、後の研磨工程を減速させるためのストッパ膜を積層する工程とを備える。また、製造方法は、ストッパ膜、メモリセル層、及び第1配線層をエッチングする工程と、ストッパ膜、メモリセル層、及び第1配線層を層間絶縁膜により埋め込んだ後、ストッパ膜に達するまで研磨する工程と、ストッパ膜及び層間絶縁膜に窒化処理を実行して、ストッパ膜及び層間絶縁膜の表面にそれぞれ調整膜及びブロック膜を形成する工程とを備える。そして、製造方法は、調整膜の上方に、エッチングされた第1配線層と交差して各交差部にメモリセルが配置されるように、第2配線層を形成する工程を備える。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体デバイス

【課題】軽量であり、かつ強固な信頼性を備えた半導体デバイスを提供する。

【解決手段】集積回路チップは、プラスチックの基板101と、基板101上に配されたポリマー誘電体103と、電極同士の間に形成された有機半導体材料112および受動層114の少なくとも1つのを含むアクティブデバイス104と、少なくとも1つのアクティブデバイス104に隣接する導電性ポリマー106および/または108とを備えている。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】半導体と金属の反応速度を制御してメモリセル領域と周辺回路領域とのシリサイド反応の差による不具合を解消する不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】シリコン基板1の上面にゲート絶縁膜4、第1の導電膜5を形成し、これらをエッチングして素子分離絶縁膜2を埋め込み形成する。電極間絶縁膜6、ゲルマニウム膜7aを形成する。周辺回路領域のゲート電極PGの電極間絶縁膜6に開口6aを形成し、この上に多結晶シリコン膜9aを形成する。ゲート電極MG、PGおよび容量性素子Capの分離加工後に層間絶縁膜10を埋め込む。多結晶シリコン膜9aの上部を露出させ、金属膜を形成してシリサイド化をする。この時、メモリセル領域ではシリサイドが速く進行するが、ゲルマニウム膜7aに達するとジャーマナイド反応は遅くなり、その間に周辺回路領域のシリサイド反応を促進させることができる。

(もっと読む)

21 - 40 / 152

[ Back to top ]