Fターム[5F083JA60]の内容

Fターム[5F083JA60]に分類される特許

61 - 80 / 2,015

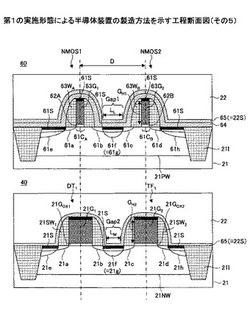

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル特性の向上、およびトランジスタ特性の劣化の抑制を図る。

【解決手段】半導体層10上に、第1絶縁膜11を形成する。第1領域における第1絶縁膜上に、表面に酸化膜15が形成された第1導電膜18を形成する。第1領域における第1導電膜上および第2領域における第1絶縁膜上に、第2導電膜19を形成する。第2導電膜上に、第2絶縁膜21を形成する。第2絶縁膜上に、第3導電膜25を形成する。第1領域における第3導電膜および第2絶縁膜の一部を貫通させて第2導電膜を露出させる。第2導電膜および第3導電膜の表面に形成された第1自然酸化膜23を除去する。第3導電膜上および第1領域における第2導電膜上に、第4導電膜27を形成する。第4導電膜上に金属層30a,30bを形成して、第4導電膜、第3導電膜、および第1領域における第2導電膜をシリサイド化する。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】メモリセルに含まれる整流素子の特性を向上した不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1方向にそれぞれ延在する複数の第1導電層と、第1方向と非平行な第2方向にそれぞれ延在し、第1方向と直交する第3方向に第1導電層と離間して設けられた複数の第2導電層と、複数の第1導電層と、複数の第2導電層と、のそれぞれの間に設けられ、多結晶半導体を含む整流素子と、第3方向に整流素子と積層された可変抵抗素子と、を有するメモリセルと、を含む不揮発性記憶装置の製造方法である。この不揮発性記憶装置の製造方法は、非晶質半導体膜を含み、整流素子となる整流素子材料膜を形成する成膜工程と、整流素子材料膜を加熱する加熱工程と、加熱工程によって加熱された整流素子材料膜をパターニングして半導体層を含む整流素子を形成するパターニング工程と、を備える。

(もっと読む)

半導体メモリ装置およびその製造方法

【課題】消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供する。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

相変化メモリ及びその製造方法

【課題】相変化記録材料から熱を急速に拡散させるための構造を有する相変化メモリとその製造方法を提供する。

【解決手段】層間絶縁膜(10、20、30)内に設けられた複数の導電プラグ(12、14)と、複数の導電プラグの夫々に接して設けられた相変化記録材料膜(16)と、相変化記録材料膜に接して設けられた上部電極(18)と、複数の導電プラグに接しないように導電プラグの側面領域に設けられた放熱のための金属材料部(22)と、を有する相変化メモリ。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】比較的高い抵抗率を持つ導電体を電極に用いた場合でも、高信頼な抵抗変化素子を実現する。

【解決手段】不揮発性半導体記憶装置は、第1配線54と、第2配線55と、一端を前記第1配線54に、他端を前記第2配線55にそれぞれ電気的に接続されたメモリセル40とを具備する。メモリセル40は、抵抗値の変化で情報を記憶する抵抗変化層41と、抵抗変化層41の両端にそれぞれ接続され、貴金属を含まない第1電極51及び第2電極52とを備える。第1電極51は、外側電極43と、外側電極43と抵抗変化層41との間に設けられた界面電極42とを含む。界面電極42の膜厚は、外側電極43の膜厚よりも薄い。界面電極42の抵抗率は、外側電極43の抵抗率よりも高い。第1電極51の抵抗値Rsは、抵抗変化層52の低抵抗状態の抵抗値Ronよりも低い。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】相変化膜の組成が変わることを抑えつつ、基板の凹部に対する相変化膜の埋め込み性を高めることのできる相変化メモリの形成方法、及び相変化メモリの形成装置を提供する。

【解決手段】相変化メモリの形成に際し、金属カルコゲナイドターゲットをスパッタして絶縁膜23の上面23s及びホール23h内に相変化膜24を形成する。次いで、相変化膜24を覆うキャップ膜25を形成する。更に、相変化膜24を加熱して、相変化膜24によってホール23hを埋め込むリフローを行う。キャップ膜25は、絶縁膜23よりも相変化膜24に対する濡れ性が低い材料で形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

分子メモリ装置の製造方法

【課題】LSIプロセスによって製造可能な分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、前記第1配線層上に犠牲膜を形成する工程と、前記第1配線層上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料によって形成された複数本の芯材を形成する工程と、前記芯材の側面上に第2配線を形成する工程と、前記犠牲膜における前記第2配線の直下域に相当する部分を除去する工程と、前記第1配線と前記第2配線との間に、メモリ材料となる高分子を埋め込む工程と、前記芯材間であって前記第2配線間の空間に絶縁部材を埋め込む工程と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

61 - 80 / 2,015

[ Back to top ]