Fターム[5F092CA02]の内容

Fターム[5F092CA02]に分類される特許

1 - 20 / 216

被膜部材の製造方法

【課題】より高い特性を有する膜体を形成する。

【解決手段】被膜部材10の製造方法は、スパッタリングターゲット部材を用い、スパッタリング処理によって被処理部材11に膜体12を形成する形成工程、を含むものである。この形成工程では、1又は複数のスパッタリングターゲット部材を用い、Mg、Al、O及びNの元素を含む膜体12を被処理部材11の表面に形成する処理を行う。ここで、スパッタリングターゲット部材は、Mg、Al、O及びNの全てが含まれていれば、どのような形態でも構わず、スパッタリングターゲット部材を1種用いるものとしてもよいし、スパッタリングターゲット部材を複数種用いるものとしてもよい。被処理部材11に形成された膜体12には、Mg、Al、O及びNが含まれている。

(もっと読む)

装置、センサおよびセンサの製造方法

【課題】装置、センサおよびセンサの製造方法を提供する。

【解決手段】さまざまな実施の形態が、概して所定の第1の形態を有する減結合層で構築された磁気センサに向けられる。磁気自由層は、減結合層に接して隣り合うように蒸着可能であり、減結合層は、処置得の第2の形態を有する少なくとも第1のサブ層を有するように構成された磁気自由層を有する。

(もっと読む)

磁気メモリ構造およびトンネル磁気抵抗効果型再生ヘッドならびにそれらの製造方法

【課題】十分に高い抵抗変化率および絶縁破壊電圧を確保しつつ、安定した製造に適した磁気トンネル接合素子を備えた磁気メモリ構造を提供する。

【解決手段】この磁気メモリ構造は、基体上に、第1シード層と導電層とを順に有する下部電極と、導線としての上部電極と、下部電極と上部電極との間に配置され、かつ、下部電極の側から順に、下部電極と接すると共に窒化タンタルを含む第2シード層と、反強磁性ピンニング層と、ピンド層と、トンネルバリア層と、磁化自由層と、上部電極と接するキャップ層とを有する磁気トンネル接合素子とを備える。窒化タンタルは、窒素プラズマをタンタルのターゲットに衝突させる反応性スパッタリング処理によって形成されたものである。

(もっと読む)

スパッタリングターゲット及びそれを用いた磁気メモリの製造方法

【課題】磁気トンネル接合素子のMR比を向上させることが可能なスパッタリングターゲット、及びそれを用いた磁気メモリの製造方法を提供する。

【解決手段】MgOを主成分とし、厚さが3mm以下であるターゲット本体10を備えることを特徴とするスパッタリングターゲット、及びそれを用いた、MR比を向上させることができる磁気メモリの製造方法である。

(もっと読む)

強磁性トンネル接合素子

【解決課題】 磁場書き込み方式MRAM、および、スピン注入磁化反転方式MRAMにおいても、書き込みに必要な電流値を小さくすることが可能な強磁性トンネル接合素子を提供する。

【解決手段】 順に、強磁性層を含む複数の層からなる強磁性自由層2と、絶縁層3と、強磁性層を含む複数の層からなる強磁性固定層4とを積層した構造を有し、前記強磁性自由層2が、該強磁性自由層2の飽和磁化を下げる働きを有する添加元素を、前記絶縁層3と接しない側において前記絶縁層3と接する側よりも多く含む強磁性トンネル接合素子1である。

(もっと読む)

薄膜磁気センサ及びその製造方法

【課題】水分透過量が小さいSi系絶縁膜が回路表面に形成されており、Si系絶縁膜の密着性及び耐クラック性に優れた薄膜磁気センサ及びその製造方法を提供すること。

【解決手段】以下の工程を備えた薄膜磁気センサの製造方法及びこの方法により得られる薄膜磁気センサ。(1)基板表面に薄膜ヨーク、GMR膜、電極及び配線を備えた素子部を形成する素子部形成工程。(2)少なくとも電極の表面の全部又は一部を含む領域(薄膜ヨーク、GMR膜及び配線の表面を除く)にフォトレジスト膜を形成するフォトレジスト膜形成工程。(3)基板の表面にAl2O3膜を形成するAl2O3膜形成工程。(4)Al2O3膜の表面に、Cat−CVD法を用いてSi系絶縁膜を形成するSi系絶縁膜形成工程。(5)フォトレジスト膜、並びに、フォトレジスト膜の上に形成された余分なAl2O3膜及びSi系絶縁膜を除去する除去工程。

(もっと読む)

磁気抵抗効果素子、およびその製造方法

【課題】CCP−CPP素子のMR変化率を向上させる。

【解決手段】磁化が実質的に一方向に固着された磁化固着層と、前記磁化固着層と対向するようにして形成され、磁化が外部磁界に対して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に位置し、絶縁層、及びこの絶縁層を層方向に電流を通過させる導電体とを有する電流狭窄層を含むスペーサ層と具える磁気抵抗効果素子において、前記磁化固着層の層中、前記磁化自由層の層中、前記磁化固着層及び前記スペーサ層の界面、並びに前記磁化自由層及び前記スペーサ層の界面の少なくとも一か所に、Si、Mg、B、Alを含む機能層を設ける。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

スピネルフェライト薄膜の製造方法

【課題】積層構造の中にスピネルフェライト薄膜を配置したスピンフィルタ効果素子において、スピネルフェライト薄膜下部の金属電極層の酸化および下部界面の熱拡散を抑制し、上部界面の大気成分による汚染を排除しつつ、(100)優先配向したスピネルフェライト薄膜を製造する方法を提供する。

【解決手段】基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

(もっと読む)

磁気抵抗素子、その製造方法、及び、半導体記憶装置

【課題】 磁気抵抗素子、その製造方法及び半導体記憶装置に関し、磁気抵抗素子の熱安定性指標Δを応力制御により大きくすることを目的とする。

【解決手段】 下部電極上に前記下部電極側から順に設けた反強磁性層、ピンド層、トンネル絶縁膜、フリー層、キャップ層、エッチングストッパー膜、ハードマスク及び上部電極と、前記少なくともフリー層の側面に設けた絶縁膜を有する磁気抵抗効果素子のエッチングストッパー膜の応力とフリー層の磁歪定数との積を負にする。

(もっと読む)

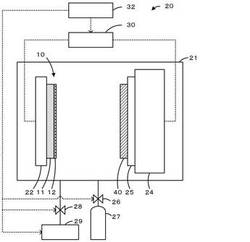

スパッタ成膜装置

【課題】非晶質磁性膜上に形成される薄膜の結晶配向性を高めることが可能なスパッタ成膜装置を提供する。

【解決手段】非晶質磁性膜を有した基板Sが収容されて希ガスが供給される真空槽11と、前記真空槽11に設けられた接地電極であるシャッタ22と、前記真空槽11内に配置されたMgOターゲットTに接続されたターゲット電極を内蔵するカソード18と、高周波電力を前記ターゲット電極に出力する高周波電源GEと、前記MgOターゲットTと前記高周波電源GEとの間に直列に接続されたインピーダンス整合器20とを備えるスパッタ成膜装置10であって、前記シャッタ22に流れる電流値を変更する可変キャパシタ26が、前記インピーダンス整合器20に対する前記MgOターゲットT側に、前記MgOターゲットTと前記シャッタ22とから構成される負荷25に対して並列に接続されている。

(もっと読む)

スパッタリング装置、及び電子デバイスの製造方法

【課題】短時間で薄膜を積層させる場合であっても、スループットを損なうことなく効率的に上記積層を実現可能なスパッタリング装置、及び電子デバイスの製造方法を提供すること。

【解決手段】本発明の一実施形態に係るスパッタリング装置は、回転可能な基板ホルダー103と、基板ホルダー130に対して斜めに配置されたターゲットホルダー107a〜107dと、ターゲットホルダーと基板ホルダーの間に設けられ、回転軸Xに対して2回対称に配置された2個の孔を有する第1シャッター115および第2シャッター116とを備える。ターゲットホルダー107a、107cは、回転軸Xに対して2回対称な位置に配置される第1群のターゲットホルダーであり、ターゲットホルダー107b、107dは、第1群のターゲットホルダー同士の間に回転軸Xに対して2回対称に配置される第2群のターゲットホルダーである。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】複数のトンネル接合素子の間隔を短縮すること。

【解決手段】上面に凹部26が形成された下地層24と、前記凹部の内面と前記凹部の両側の下地層上とに形成された下部電極28と、前記凹部の両側の前記下部電極上に形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に形成され、前記凹部の上方において電気的に分離された複数の上部電極40と、を具備する磁気デバイス。

(もっと読む)

磁気トンネル接合素子、その製造方法、及びMRAM

【課題】 積層構造の側方に生成された付着物の影響を受けにくい磁気トンネル接合素子が求められている。

【解決手段】 基板上に形成された下部電極の一部の領域の上に、下部電極とはエッチング特性が異なる導電材料で形成されたバッファ層が配置されている。バッファ層の上に、アモルファスの強磁性材料で形成された第1磁化自由層が配置されている。第1磁化自由層の上に、結晶化した強磁性材料で形成された第2磁化自由層が配置されている。第2磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が固定された磁化固定層が配置されている。磁化固定層の上に上部電極層が配置されている。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】磁気トンネル接合に導入されるダメージによる磁気デバイスの劣化を抑制すること。

【解決手段】上面に凹部26を備える下部電極28と、前記下部電極の前記凹部の内面と前記凹部外の前記下部電極上とに形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に、前記磁気トンネル接合層の側面に達しないように形成された上部電極40と、を具備する磁気デバイス。

(もっと読む)

強磁性積層構造及びその製造方法

【課題】大きなスピン偏極電流を得る。

【解決手段】Si単結晶基板上に単結晶のMgO層が成長し、格子整合している。更にこの上に強磁性金属層が形成されている。Si単結晶基板の(100)面上に形成されたMgO層の成長面は(100)面である。ここで、Si単結晶基板とMgO層の界面において、Si(100)[110]方向とMgO(100)[100]方向とが平行となっている。図2(a)はSi(100)面、(b)はMgO(100)面、(c)はこれらの2つの面が格子整合した状態を示す。Si(100)面(a)はSi原子111だけで構成され、MgO(100)面(b)はMg原子121と酸素(O)原子122で構成される。ここでは、Si(100)面上においてMgO(100)面が成長し、図2(c)に示されるように、界面においてSi(100)[110]方向とMgO(100)[100]方向とが平行となっている。

(もっと読む)

磁気抵抗素子

【課題】従来よりも高いMR比を持った磁気抵抗素子とその製造方法を提供する。

【解決手段】本発明は、磁気ディスク駆動装置の磁気再生ヘッド、磁気ランダムアクセスメモリの記憶素子及び磁気センサーに用いられる磁気抵抗素子、好ましくは、トンネル磁気抵抗素子(さらに好ましくは、スピンバルブ型トンネル磁気抵抗素子)に関し、基板、トンネルバリア層、Co(コバルト)Fe(鉄)合金からなる強磁性層及びB(ボロン)を含有した非磁性金属層を有する磁気抵抗素子。

(もっと読む)

スピン偏極率制御方法

【課題】従来物質固有の特性として取り扱われてきたスピン偏極率を制御する手法とその素子構造を提案し、従来にない新しい機能性デバイスの基本要素技術を提供する。

【解決手段】強誘電体(A)層上に、該強誘電体(A)と格子不整合率が8%以下である強磁性体(B)層をヘテロ接合してなり、該強誘電体(A)に電圧を印加させて、強誘電体(A)と強磁性体(B)の接合界面に生じる歪みにより、強磁性体(B)のスピン偏極率を変化させることを特徴とする強磁性体のスピン偏極率制御方法。

(もっと読む)

磁気センサ

【課題】 磁界感度異方性、広動作磁界および出力直線性に優れた磁気センサを提供すること。

【解決手段】 絶縁基板20と、絶縁基板20の表面に形成されたGMR素子22a〜22dと、絶縁基板20の裏面に配置されたバイアス磁石24とで磁気センサ20を構成した。そして、GMR素子22a〜22dを一方側と他方側との間を折り返しながら延びる線状のグラニュラ薄膜で構成し、バイアス磁石24によるバイアス磁界をGMR素子22a〜22dの線状が延びる長手方向に印加した。また、GMR素子22a〜22dを構成するグラニュラ薄膜を、Agからなる母相中に、FeCoからなる微粒子を分散させて構成した。

(もっと読む)

1 - 20 / 216

[ Back to top ]