Fターム[5F101BA12]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858)

Fターム[5F101BA12]の下位に属するFターム

埋め込みFG、溝 (45)

CG側壁 (37)

FGの突起 (84)

複数FG(単一メモリセル内) (90)

FG接続 (271)

PN接合(FG内の) (5)

Fターム[5F101BA12]に分類される特許

141 - 160 / 326

不揮発性半導体メモリ

【課題】SOI領域内に特性の均質なメモリセルを作製できるNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、SOI領域SAとエピタキシャル領域EAを表面に有する半導体基板1と、SOI領域SA上に配置される埋め込み酸化膜2と、埋め込み酸化膜2上に配置されるSOI層3と、SOI層3上に配置される複数のメモリセルMC1〜MCnと、エピタキシャル領域EAに配置されるエピタキシャル層4と、エピタキシャル層4上に配置される選択ゲートトランジスタSGD,SGSとを具備し、SOI層3は、微結晶層からなることを備える。

(もっと読む)

マルチレベル構造を有する記憶装置

【課題】記憶容量が記憶素子における表面集積度の増大に、そして表面寸法に単にリンクしていない装置を提案する。

【解決手段】略0.01(Ω・cm)−1未満の伝導度を有する第1層(4a)と、略1(Ω・cm)−1より上の伝導度を有する第2層(4b)との交互配置で形成される層(4a、4b)のスタック(4)、これらの層のスタック中に配置されて、このスタック(4)における各層(4a、4b)を貫通する複数の柱(6、6a、6b)、可動マイクロスパイク(22)のネットワークを備える前記柱の端部に電圧を印加する手段、を備え、各々の柱は、半導体材料の部分及びスタックから電気的に絶縁された少なくとも1つの電荷貯蔵層(10a、10b)によって囲まれた半導体材料(8a、8b)の少なくとも一部で製造される、データ記憶装置(100)。

(もっと読む)

半導体装置

【課題】特に、横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔52の外側に位置し、該配線層26の延伸方向と交差する分岐部28を有することで該開孔52の幅と同一以上の幅を有する第2部分26Bと、を含むパターンを有し、

前記分岐部28において、前記遮光壁50の外側を向いた面は、その表面に凸部を有する。

(もっと読む)

ナノスケール浮遊ゲートおよび形成方法

半導体基板(102)の上にあるトンネル誘電体層(104)を含むメモリセル(100)が提供される。メモリセルは、トンネル誘電体層の上にある第一の部分(106)と、第一の部分からのびるナノロッドの形の第二の部分(116)とを持つ浮遊ゲートも含む。加えて、制御ゲート層(122)は、ゲート間誘電体層(120)によって浮遊ゲートから分離される。  (もっと読む)

(もっと読む)

半導体装置

【課題】金属または金属シリサイドを含む制御電極と蓄積電荷層との間に設けられる絶縁膜の薄膜化に伴う絶縁耐圧不足およびリーク電流の増加を抑制できる半導体装置を提供すること。

【解決手段】複数のメモリセルが並んだメモリセルアレイを含む半導体装置であって、前記メモリセルは、半導体基板上に設けられた第1の絶縁膜11と、第1の絶縁膜11上に設けられた蓄積電荷層12,18と、蓄積電荷層12,18上に設けられた第2の絶縁膜19−23と、蓄積電荷層12,18上に第2の絶縁膜19−23を介して設けられ、金属シリサイドを含む制御電極29とを具備してなり、前記メモリセルのチャネル幅方向において、制御電極29の下部角部24は、半導体で構成され、かつ、前記金属を含まないことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロール・ゲートによるチャネルの制御性を向上し、データを読み出す際の駆動電圧の低減及び駆動速度の高速化を可能とした半導体装置およびその製造方法を提供する。

【解決手段】Si層5の側面及び上面に形成されたトンネルゲート絶縁膜11及びゲート絶縁膜15と、これらゲート絶縁膜11、15中に埋め込まれて周囲から絶縁されたフローティング・ゲート13と、ゲート絶縁膜11、15を介して、Si層5の一方の側面から上面を通って他方の側面にかけて形成されたコントロール・ゲート(即ち、Π型ゲート電極)17と、を備え、Y−Y´線に沿った断面視で、Si層5の側面とコントロール・ゲート17との間にはフローティング・ゲート13が配置されており、且つ、Si層5の上面とコントロール・ゲート17との間にはフローティング・ゲート13が配置されていない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】ビット線の低抵抗化と装置の微細化を同時に実現する不揮発性半導体記憶装置及びその製造方法の提供。

【解決手段】ビット線が、チャネル長方向に隣接する2つの前記第1のゲート電極により共有され、チャネル幅方向に延在し、かつ前記第1のゲート電極をマスクとして自己整合的にAsを5E14〜1E15cm-2の注入量でイオン注入することで形成された第1ビット線17と、前記第1のゲート電極及び前記サイドウォールスペーサー18をマスクとして自己整合的に形成された第2ビット線からなり、前記第2ビット線が、前記第1ビット線17より深く形成され、かつ前記第1ビット線17より高い不純物濃度を有し、チャネル幅方向に隣接する2つの前記第1のゲート電極17が、その間で、かつ前記ビット線に隣接する領域にBF2を1E13〜1E14cm-2の注入量でイオン注入することで形成された素子分離拡散領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】積層ゲート電極の加工を容易にするNAND型フラッシュメモリ等の半導体装置およびその製造方法を提供する。

【解決手段】第1のゲート絶縁膜5上に浮遊ゲート電極FGとして機能し、素子分離領域Sbに対して自己整合的に構成されている第1の導電膜6、ONO膜等の第2のゲート絶縁膜7、制御ゲート電極として機能する第2の導電膜8を形成後、第1および第2の導電膜と第2のゲート絶縁膜7をゲート電極分離領域GVに沿って分離する。その後、第2の導電膜8の上に対してTi/TiN等によるバリアメタル膜9aにより下面および側面が覆われたタングステン等の金属層9bが積層されてなる第3の導電膜9が構成される。

(もっと読む)

半導体装置

【課題】 バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】 半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル幅方向に平行な一対の側面の下端近傍に形成された一対の酸化膜8aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】微細化によるメモリセル間の干渉を低減し、かつ、オフ状態でのリーク電流を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10と、半導体基板に形成された複数の素子分離領域STIと、隣り合う素子分離領域間に設けられた素子形成領域AAであって、素子分離領域の隣接方向の断面において素子形成領域の側部の一部分の幅が該素子形成領域の上面の幅よりも狭い窪みCを有する素子形成領域と、素子形成領域上に設けられた第1のゲート絶縁膜20と、第1のゲート絶縁膜上に設けられたフローティングゲート電極FGと、フローティングゲート電極上に設けられた第2のゲート絶縁膜30と、第2のゲート絶縁膜上に設けられたコントロールゲート電極CGとを備え、素子分離領域の隣接方向の断面においてフローティングゲート電極の上辺の幅がフローティングゲート電極の下辺の幅よりも狭い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート間絶縁膜より下方の膜を所望の特性を得つつ構成できるようにする。

【解決手段】X方向およびY方向に複数並設された浮遊ゲート電極FGの上を渡って第2のゲート絶縁膜7が連続的に形成されている。このため、第2のゲート絶縁膜7上のゲート電極分離領域GVに対して層間絶縁膜Zを埋込むときには第2のゲート絶縁膜7の上面まで埋込めばよい。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み効率の向上とメモリ容量の大容量化を実現できる不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルを3次元構造化し、ドレイン付近にバンド間トンネリングによるホットエレクトロンを発生させ、このホットエレクトロンを3次元化によりドレイン端に対して大きな立体角で配置される電荷蓄積層に注入してビットデータの書き込みを行う

。これにより従来のバンド間ホットエレクトロン注入を用いた書き込み方式に比べ書き込み効率が向上し、3次元化、多段積層化により大容量化を実現する。

(もっと読む)

リセスタイプの制御ゲート電極を備える半導体メモリ素子

【課題】リセスタイプの制御ゲート電極を備える半導体メモリ素子を提供する。

【解決手段】半導体基板と、半導体基板の内部にリセスされて形成された少なくとも一つの制御ゲート電極と、少なくとも一つの制御ゲート電極の側壁と半導体基板との間に介在された少なくとも一層のストレージノード膜と、少なくとも一層のストレージノード膜と半導体基板との間に介在された少なくとも一層のトンネリング絶縁膜と、少なくとも一層のストレージノード膜と少なくとも一つの制御ゲート電極との間に介在された少なくとも一層のブロッキング絶縁膜と、少なくとも一つの制御ゲート電極の側壁を取り囲むように、少なくとも一層のトンネリング絶縁膜下の半導体基板の表面付近に相互分離されるように形成された第1及び第2チャンネル領域とを備え、少なくとも一層のブロッキング絶縁膜の誘電率は、少なくとも一層のトンネリング絶縁膜の誘電率より大きいことを特徴とする。

(もっと読む)

低次元構造体のカプセル化、転移方法

【課題】グループ内の低次元構造体の数、グループのアスペクト比を、より正確にコントロールすることができる。

【解決手段】低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とを第1の基板に形成する工程を含む低次元構造体のカプセル化方法。低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とはマトリックス(5)に別々にカプセル化される。カプセル化後、低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とを分離してもよい。各グループは、その後、例えば第2の基板(7)に移動するなどの処理が行われる。グループ内の低次元構造体の数、グループのアスペクト比は、低次元構造体が形成される際に決定され、パターニング法を使って決定されていた従来の方法に比べて、より正確にコントロールすることができる。

(もっと読む)

浮遊ゲートNANDフラッシュメモリ用のゲート注入を用いるセル動作方法

【課題】浮遊ゲートに対して効率的なFNトンネリングを可能にするように、浮遊ゲート装置を動作させること。

【解決手段】フラッシュメモリ素子上で動作を行う方法であって、浮遊ゲートと制御ゲートの間にゲート結合率が0.4未満である場合に用いられる。電位は、制御ゲートを介して印加する必要がある。電子は、制御ゲートから浮遊ゲートに注入されるか、または浮遊ゲートから制御ゲートに放出される。注入および放出に対応した動作は、素子内に提供されるシリコンチャネルの性質によって決定される。この方法には特に、バルク結合FinFET状構造を用いる素子が適している。この方法は特に、NANDアレイ内のセル上で用いる場合にも適している。

(もっと読む)

エージングデバイス及びその製造方法

【課題】エージングデバイスの寿命を正確にコントロールする。

【解決手段】本発明の例に関わるエージングデバイスは、上面が半導体基板11の上面よりも上にある素子分離絶縁層12と、素子分離絶縁層12により分離される第1及び第2素子領域13,14と、第1素子領域13内の半導体基板11内に形成される第1及び第2拡散層15a,15b,16a,16bと、第1及び第2拡散層間15a,15b,16a,16bの半導体基板11上に形成される第1ゲート絶縁膜19と、第2素子領域14内の半導体基板11上に形成される第2ゲート絶縁膜19と、第1及び第2ゲート絶縁膜19上に形成され、第1素子領域13から第2素子領域14まで跨って形成されるフローティングゲート電極20とを備え、第1及び第2拡散層15a,15b,16a,16bの最も深い部分は、素子分離絶縁層12から離れている。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリアによる書き込み・消去を行うに当たり、消去後の閾値電圧のばらつきを小さくでき、且つ、誤動作を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】スプリットゲート構造の不揮発性半導体記憶装置100であって、ソース130を、ドレイン120との間にチャネル領域125を構成する基部130aと、基部130aから延設された延設部130bとにより構成し、浮遊ゲート電極160を、第1ゲート絶縁膜150aを介して、ドレイン120側に偏ってチャネル領域125上に配置されるドレイン対向部160aと、第1ゲート絶縁膜150aを介してソース130の延設部130b及び/又はその近傍上に配置されるソース対向部160bと、ドレイン対向部160aとソース対向部160bを連結する連結部160cとにより構成した。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】セル間干渉効果を抑制しつつ電極間絶縁膜容量の減少を抑制可能な半導体記憶装置を提供する。

【解決手段】ビット線方向に沿った断面において、第1導電膜14、第1導電膜14を挟んで互いに対向して配置された第1側壁絶縁膜40、並びに、第1側壁絶縁膜40及び第1導電膜14上に設けられた第2導電膜26を含む浮遊ゲート電極と、第2導電膜26上の電極間絶縁膜28と、電極間絶縁膜28上の第3導電膜30、及び第3導電膜30上の第4導電膜34を含む制御ゲート電極とを備えるメモリトランジスタを複数個配置する。

(もっと読む)

半導体記憶装置

【課題】トンネル絶縁膜の膜質の劣化を防止し、且つメモリセルアレイ及び周辺回路の動作速度の低下を防止する不揮発性半導体記憶装置を提供する。

【解決手段】複数個のメモリセルトランジスタ及びそのメモリセルトランジスタを選択する選択トランジスタを配置したメモリセルアレイと、メモリセルアレイを制御する周辺回路とを備える半導体記憶装置であって、メモリセルトランジスタは、ゲート絶縁膜12と、ゲート絶縁膜12上の浮遊ゲート電極13と、浮遊ゲート電極13上に配置され、半導体記憶装置のデータ書込み及びデータ消去動作における電界印加時の通過電荷量がゲート絶縁膜12より多い電極間絶縁膜14と、電極間絶縁膜14上の制御ゲート電極15とを備える。

(もっと読む)

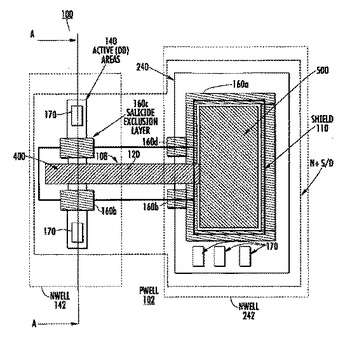

フローティングゲートトンネリング素子構造体のシールド

フローティングゲートトンネリング素子をシールドする方法とその構造体。標準的なCMOSプロセスを用いて、電界酸化物に囲まれた基板内に形成された第1および第2のドープウェル領域により定義される2つの活性領域内のゲート酸化物上にフローティングゲートを配置する工程と、前記フローティングゲートを囲むようにフローティングゲートシールド層を形成する工程を含む方法。前記フローティングゲートは、前記第1のドープウェル領域内の活性領域上の第1のフローティングゲート部および前記第2のドープウェル領域内の活性領域上の第2のフローティングゲート部を含む。前記第1のドープウェル領域と前記第1のフローティングゲート部との間にファウラーノルドハイムトンネリングのための適当な電圧カップリングが発生しうるよう、前記第1のフローティングゲート部は第2のフローティングゲート部より実質的に小さくなっている。トンネリングの方向は、前記ドープウェル領域の1つに高電圧を印加することにより決定される。  (もっと読む)

(もっと読む)

141 - 160 / 326

[ Back to top ]