Fターム[5F102GD04]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421)

Fターム[5F102GD04]の下位に属するFターム

ヘテロゲート (33)

Fターム[5F102GD04]に分類される特許

161 - 180 / 388

半導体装置及び半導体装置の製造方法

【課題】半導体装置のリーク電流を低減する。

【解決手段】GaAs層とInGaP層とが積層された構造を有する半導体装置において、GaAs層にp型不純物をドーピングする。その結果、GaAsの伝導帯が持ち上げられ、フェルミ準位より高くなる。従って、電子蓄積が抑制され、ゲートリーク電流を減少することが可能となる。

(もっと読む)

ゲート駆動回路

【課題】双方向スイッチを採用したインバータでは、ゲート駆動回路を形成する際に基準電位が互いのゲート端子で異なる。特にハイサイド側のゲート駆動回路を簡易な回路構成で基準電位をバス電圧を上回る電位とすることを目的とする。

【解決手段】第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を直列接続したハーフブリッジ回路に適用するゲート駆動回路であり、第一ゲート端子2を常時オンとする保持回路19を備え、簡易な回路構成、かつ低コストで第一ゲート端子2を常時オン、第二ゲート端子3をPWM制御する低損失な駆動を可能としたゲート駆動回路を実現することができる。

(もっと読む)

窒化物半導体装置

【課題】 ノーマリオフ特性を備えている窒化物半導体装置2を提供する。

【解決手段】 窒化物半導体装置2では、アンドープのGaNを材料とする窒化物半導体下層8の表面に、アンドープのAlGaNを材料とする窒化物半導体層10が積層されている。窒化物半導体層10は、窒化物半導体下層8よりも大きなバンドギャップを備えており、窒化物半導体下層8に対してヘテロ接合している。窒化物半導体層10の表面にはゲート絶縁膜16が形成されている。ゲート絶縁膜16は、窒化アルミニウム膜15で形成されている部分と、酸素又はシリコンを含む絶縁物質14で形成されている部分を含んでいる。窒化アルミニウム膜15が形成されている範囲W2はゲート電極18が形成されている範囲W1に含まれる関係にある。

(もっと読む)

電力用半導体装置

【課題】トランジスタの逆モード動作の特性改善が可能な超接合静電誘導型トランジスタを有する電力用半導体装置を提供する。

【解決手段】n型ドリフト層12と、n型ドリフト層12中に膜面に沿う方向に周期的に配置され、膜面に垂直な方向に伸長した複数の柱状のp型ゲート・ドリフト層14と、n型ドリフト層12の一方の側の表面に設けられn型ドリフト層12と電気的に接続されたドレイン電極23と、n型ドリフト層12の他方の側の表面に設けられた低抵抗のn+型ソース層16と、n+型ソース層16の表面に接するように設けられたソース電極21と、p型ゲート・ドリフト層14に接続されたゲート電極25とを有するノーマリオン型のSJ−SIT10と、ソース電極21とゲート電極25との間に接続され、ゲート電極25の電圧がソース電極21の電圧を超えないように維持する抵抗33とを備えている。

(もっと読む)

トランジスタ

【課題】 ノーマリーオフ型であるとともに、ゲート閾値電圧のばらつきが小さいHEMT型のトランジスタを提供する。

【解決手段】 このトランジスタは、p型領域と、チャネル領域と、バリア領域と、絶縁膜と、ゲート電極を備えている。チャネル領域は、n型またはi型であり、p型領域の表面に接しており、第1チャネル領域と第2チャネル領域を有している。バリア領域は、第1チャネル領域の表面とヘテロ接合している。絶縁膜は、第2チャネル領域の表面、及び、バリア領域の表面に接している。ゲート電極は、絶縁膜を介して第2チャネル領域及びバリア領域に対向している。第1チャネル領域と第2チャネル領域は、電流経路において直列に配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を落とすことなくチャネル抵抗を低減したノーマリオフ型接合FETを提供する。

【解決手段】炭化珪素からなる基板1を用いて形成した接合FETにおいて、チャネル領域(第2エピタキシャル層3)の不純物濃度をドリフト層となる第1エピタキシャル層2の不純物濃度よりも高くする。チャネル領域は、チャネル幅が一定の領域7Aと、その下部でドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bとから形成し、第1エピタキシャル層2とチャネル領域との境界は、ドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bに位置するようにする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】p型コンタクト抵抗を低減でき、素子のスイッチングスピードを下げないようにすることができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6のうち第1〜第3コンタクトホール12〜14から露出した部位に、炭化珪素とAlとNiとが反応してそれぞれ形成された合金層15が設けられている。この合金層15におけるAlとNiとの元素組成比は1:4.6〜1:10.6であり、合金層15の厚さは20nm以上100nm以下になっている。これにより、合金層15と半導体基板6とがオーミック接触となり、低いコンタクト抵抗率を得ることが可能となる。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】JFETが形成されるセル領域とダイオード形成領域との間の絶縁耐圧を向上でき、耐圧の最適設計が行える構造のSiC半導体装置を提供する。

【解決手段】電界緩和領域R3に備えたp型領域9bとn型領域8bとにより構成されるPN分離部により、セル領域R1とダイオード形成領域R2の間の素子分離を行う。これにより、トレンチ内に酸化膜を配置して素子分離を行う場合と比べて、素子分離用の酸化膜が絶縁破壊されることが無いため、JFETが形成されるセル領域R1とダイオード形成領域R2との間の絶縁耐圧を向上できる。このため、素子分離に酸化膜を用いる場合と比べて耐圧の最適設計を行うことが可能となる。

(もっと読む)

電界効果トランジスタ

【課題】電流容量および耐電圧を大きくしたノーマリオフの縦型構成の電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、半導体基板10と、半導体基板10に積層された窒化物系III−V族化合物半導体層20と、窒化物系III−V族化合物半導体層20から積層方向に交差する横方向へ成長した横方向成長領域22と、半導体基板10の裏面に形成されオーミック性を有する第1電極31(ドレイン電極)と、窒化物系III−V族化合物半導体層20の表面に形成されオーミック性を有する第2電極32(ソース電極)と、窒化物系III−V族化合物半導体層20の積層方向で第1電極31と第2電極32との間での電流路となる通電領域21と、横方向成長領域22に接触させて形成され通電領域21での通電状態を制御する第3電極33(ゲート電極)とを備える。

(もっと読む)

III族窒化物系化合物半導体基板とその製造方法

【課題】平面視したときに限定された範囲にp型領域が形成されているIII族窒化物系化合物半導体基板であり、p型領域とその周囲の領域との間に段差がない基板を提供する。

【解決手段】 III族窒化物系化合物半導体下層6の表面にIII族窒化物系化合物半導体を結晶成長させるに先立って、p型領域12を形成したい範囲に相当する範囲内の下層6の表面近傍にマグネシウムとアルミニウムの双方を含ませておく。下層6の限られた範囲の表面近傍にマグネシウムとアルミニウムの双方が含まれていると、その上に上層16を結晶成長したときに、結晶成長する上層16の限られた範囲にマグネシウムが移動してp型領域12になるともに、下層6に含まれているアルミニウムがマグネシウムの移動範囲を制約し、下層6におけるマグネシウムの含有範囲10と上層16におけるマグネシウムの含有範囲12をよく一致させる。

(もっと読む)

電界効果トランジスタ及び電界効果トランジスタの製造方法

【課題】T型構造のゲート電極の傘部と拡散層の間に生じる寄生容量を低減した電界効果トランジスタ及びその電界効果トランジスタの製造方法を提供する。

【解決手段】半絶縁性単結晶GaAsよりなる基板11上に、バッファ層12、第1電子供給層13、チャネル層14、第2電子供給層15、拡散層16、キャップ層17が順次積層されて半導体積層部10が形成される。そして、この半導体積層部10の表面に設けた第1絶縁膜18の下方であって、かつT型構造のゲート電極21に隣接した位置に空洞部25を設けた。

(もっと読む)

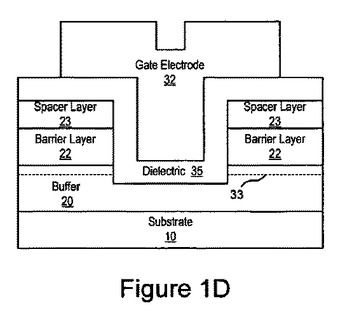

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

電界効果トランジスタ、その製造方法、及び半導体装置

【課題】電圧ストレス前後でのしきい値電圧変動が少ない高信頼性の電界効果トランジスタ、その製造方法、及び半導体装置を提供すること

【解決手段】本発明にかかるJ−FET51は、半絶縁性GaAs基板1上に形成された第1導電型のチャネル層(Siドープn型AlGaAs電子供給層3、7、アンドープAlGaAsスペーサ層4、6、アンドープInGaAsチャネル層5)と、第1導電型のチャネル層上に形成された少なくとも1層以上の半導体層からなる上層半導体層と、上層半導体層に設けられたリセス内、又は上層半導体層の上に形成された第2導電型の半導体層(Cドープp+−GaAs層18)と、第2導電型の半導体層上に接触して設けられたゲート電極19と、上層半導体層の上に接触して設けられた窒化膜16と、窒化膜16上に形成され、窒化膜16よりも膜厚の厚い酸化膜17とを含むゲート絶縁膜と、を備えるものである。

(もっと読む)

伝導を高めた非パンチスルー半導体チャネルを有する半導体デバイス及びその製法

デバイスにおける電流フローが整流接合(例えば、p−n接合又は金属半導体接合)の間で制限される、半導体デバイスが記載される。デバイスは、非パンチスルー挙動と高められた電流伝導能力を提供する。デバイスは、接合型電界効果トランジスタ(JFETs)、静電誘導トランジスタ(SITs)接合型電界効果サイリスタ、又はJFET電流制限器などのような電力半導体デバイスである。デバイスは、炭化ケイ素(SiC)等の広バンドギャップでできている。いくつかの実施形態において、デバイスは、常時オフ型SiC垂直接合型電界効果トランジスタである。デバイス及びデバイスを備える回路を製造する方法もまた記載される。 (もっと読む)

半導体装置

【課題】基板の結晶面方位を規定して表面の微細な凹凸を抑制した炭化珪素基板上のエピタキシャル相に半導体装置を形成することによって、その電気的特性を改善する。

【解決手段】炭化珪素半導体基板上に形成する半導体装置として、基板の(000−1)面から0°超で以上1°未満傾斜した面上に成長したエピタキシャル層に、P型あるいはN型領域をイオン注入により選択的に形成して製造したダイオード、トランジスターなどとする。

(もっと読む)

双方向スイッチのゲート駆動方法およびそれを用いた電力変換装置

【課題】インバータ等に適用される半導体デバイスは、寄生ダイオードにより誘導負荷からの還流電流を通流する場合、ダイオードの順方向電圧による損失が大きくなることが懸念され、また双方向デバイスを適用した場合には、2つのゲート端子を駆動する必要があり、制御の複雑化、かつ高コストになるという課題があった。

【解決手段】第一ゲート端子2、第二ゲート端子3、ドレイン端子4、ソース端子5を備え、第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1に適用する駆動方法であり、第一ゲート端子2あるいは第二ゲート端子3の何れか一方を常時オン状態となるように制御し、還流電流を流す経路を確保しつつ、ダイオード損失を低減し、かつ2つのゲート信号数を減らし、簡易な回路構成、かつ低コストに実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】 接合型FETを簡単な製造工程で形成しながら、そのpチャネル接合型FETと同じ工程で形成することができpn接合を含む保護素子とを内蔵する半導体装置の製造方法を提供する。

【解決手段】 pチャネルFETと保護素子とを有し、化合物半導体からなる半導体装置の製造方法で、基板1上にn型チャネル層2とn+型コンタクト層3と、n型半導体層5と、p型チャネル層7とp+型コンタクト層8とを積層することにより半導体積層部10を形成し、その半導体積層部10の一部をエッチングにより除去してn+型コンタクト層3を露出させ、露出したn+型コンタクト層3の表面に接合型pチャネルFET22のゲート電極13を形成し、半導体積層部10の一部で保護素子23を形成する。

(もっと読む)

半導体装置

【課題】 チャネル層と反対導電型の半導体層を形成して接合型FETとする場合に、チャネル層の不純物濃度などの特性変動を生じさせることなく、かつ、簡単に製造することができる構造の接合型電界効果トランジスタを有する半導体装置を提供する。

【解決手段】 p型のチャネル領域3aの両側のチャネル層3上に一対のp+型コンタクト層4が設けられ、チャネル層3の下側にn+型コンタクト層4が設けられている。そして、一対のp+型コンタクト層4上にオーミックコンタクトするようにソース・ドレイン電極5が設けられ、チャネル層3の下側に設けられるn+型コンタクト層2の露出面上にオーミックコンタクトするようにゲート電極6が設けられることにより、接合型FETが形成されている。

(もっと読む)

へテロ接合を有する半導体装置とその製造方法

【課題】 オン抵抗が低減されたヘテロ接合を有する半導体装置を提供すること。

【解決手段】 半導体装置10は、窒化ガリウムの半導体下層30と、半導体下層30の表面に設けられている窒化ガリウムアルミニウムの半導体上層40と、半導体上層40の表面に設けられている絶縁ゲート部55を備えている。半導体下層30と半導体上層40は、ヘテロ接合72を構成している。半導体上層40は、マグネシウムを含むp型であることを特徴としている。

(もっと読む)

161 - 180 / 388

[ Back to top ]