Fターム[5F102GJ10]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体以外の材料 (1,158) | 絶縁体材料(ガラス、サファイア等) (1,144)

Fターム[5F102GJ10]に分類される特許

201 - 220 / 1,144

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体デバイスの製造方法およびエピタキシャル成長用の支持基板

【課題】中間層の一部が露出している支持基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まりよく製造することができる半導体デバイスの製造方法およびエピタキシャル成長用の支持基板を提供する。

【解決手段】本半導体デバイスの製造方法は、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させることができる下地基板10と、下地基板10上に全面的に配置された中間層20と、中間層20上に部分的に配置されたGaN層30aとを含み、GaN層30aと中間層20の一部とが露出している支持基板2を形成する工程と、支持基板2の中間層20が露出している部分20p,20q,20rを選択的に除去することにより、下地基板10の一部を露出させる工程と、GaN層30a上に、III族窒化物半導体層をエピタキシャル成長させる工程と、を備える。

(もっと読む)

高分子化合物、これを含む薄膜及びインク組成物

【課題】高い電荷の移動度が得られる高分子化合物を提供すること。

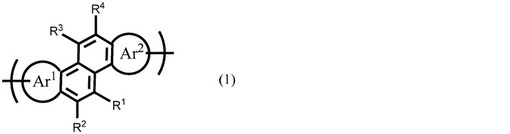

【解決手段】式(1)で表される繰り返し単位を有する高分子化合物。

[Ar1及びAr2は、芳香族炭化水素環、複素環、又は芳香族炭化水素環と複素環との縮合環である。R1、R2、R3及びR4は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、置換シリル基、非置換若しくは置換のカルボキシル基、1価の複素環基、シアノ基又はフッ素原子を示す。]

(もっと読む)

インジウムガリウムナイトライド層を有する高電子移動度トランジスタ

【課題】バッファ界面のストレスが低減した、インジウムガリウムナイトライド層を有する高電子移動度トランジスタを提供する。

【解決手段】基板104の上に形成され、ガリウムナイトライドで構成されるバッファ層108と前記バッファ層の上に形成され、インジウムアルミニウムナイトライド(InAlN)で構成された第1のバリアサブレイヤーと114、第1のバリアサブレイヤーの上に形成され、アルミニウムガリウムナイトライド(AlGaN)で構成された第2のバリアサブレイヤー116と、含む、バリア層と、第2のバリアサブレイヤーの上に形成されたソース端子120、ゲート端子124およびドレイン端子128と、を含む高電子移動度トランジスタ。

(もっと読む)

高周波半導体スイッチ

【課題】ゲート配線に良好な電圧分布を形成し、挿入損失特性およびハーモニック特性を向上した高周波半導体スイッチを提供する。

【解決手段】無線通信を切り替えるための高周波半導体スイッチに含まれる電界効果型トランジスタ50であって、基板に形成されたソース領域100と電気的に接続され、一の方向に延びるソース配線60と、基板に形成されたドレイン領域110と電気的に接続され、ソース配線と略平行に延びるドレイン配線70と、ソース配線60およびドレイン配線70の間において、ソース配線60およびドレイン配線70と略平行に延びる平行部分122を有するゲート120と、ゲート120に電圧を印加するためゲート配線80と、ゲート120およびゲート配線80を電気的に接続するゲートビア82と、を有し、平行部分122は、2つの端部126を有し、ゲートビア82から2つの端部126にそれぞれ電圧の印加の経路が形成される電界効果型トランジスタ。

(もっと読む)

応力変調III−V族半導体装置および関連方法

【課題】基板の変形を制限しつつ厚いIII−V族半導体層の成長を可能にする方法を提供する。

【解決手段】III−V族半導体装置は、基板102の上およびIII−V族半導体装置の活性領域112を支持するバッファ層110の下に配置された組成傾斜本体108を備える。組成傾斜本体108は、基板102に圧縮応力を与える第1の領域を含む。組成傾斜本体108は、第1の領域上に応力変調領域をさらに含み、その応力変調領域は基板102に引張応力を与える。

(もっと読む)

共役系化合物、並びにこれを用いた有機薄膜及び有機薄膜素子

【課題】電子輸送性に優れたn型半導体として利用可能であり、しかも溶剤への溶解性にも優れる共役系化合物の提供。

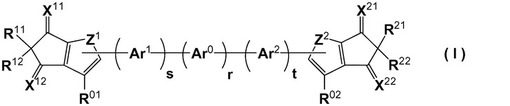

【解決手段】式(I)で表される共役系化合物。[式中、R01及びR02はアルカン骨格を含む1価の基。R11、R12、R21及びR22は水素原子、ハロゲン原子又は1価の基。X11、X12、X21及びX22は=O,=S又は=CA2(Aは水素原子、ハロゲン原子又は1価の基を示すが、その少なくとも1つは電子吸引性の基。)を示す。Z1及びZ2は−O−,−S−,−Se−,−Te−,−SO−等のいずれかの基を示す。Ar0、Ar1及びAr2は芳香族炭化水素基又は複素環基を示す。rは1〜6の整数、s及びtは0〜6の整数を示す。] (もっと読む)

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

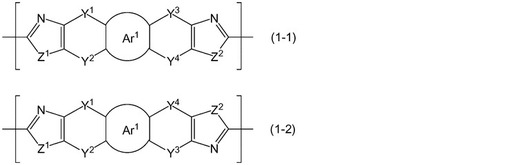

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

高電子移動度トランジスタ

【課題】ノーマリオフ特性を得つつスイッチング特性が向上した高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】窒化物半導体からなるHEMT100は、n型不純物を含むか又はアンドープの第1層103と、第1層上に設けられ第1層よりもバンドギャップエネルギーが大きい第2層105と、第2層上に設けられp型不純物を含む第3層106と、第3層上に設けられ下側から上側に向かってバンドギャップエネルギーが小さくなっている第4層107と、を有する。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制しつつ良好な結晶性の電子走行層及び電子供給層を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層3と、電子走行層3上方に形成された電子供給層4と、基板1と電子走行層3との間に形成され、AlxGa1-xN(0≦x≦1)を含むバッファ層2と、が設けられている。xの値は、バッファ層2の厚さ方向で複数の極大及び複数の極小を示し、バッファ層2中の厚さが1nmの任意の領域内では、xの値の変化量が0.5以下となっている。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体8をドライエッチングして形成した平坦表面に電極を形成してもオーミック接触させることができない。

【解決手段】p型III族窒化物半導体8の電極形成範囲をドライエッチングして溝8dを形成し、その溝8dに金属20を充填して電極を形成する。p型III族窒化物半導体8のドライエッチング面は、エッチングによって生じた欠陥によってn型化しているために、平坦平面にドライエッチングしておいて電極を形成するとオーミック接触しない。溝8dを設けておくと、欠陥が少ない溝8dの側面においてp型III族窒化物半導体8と電極がオーミック接触し、半導体と電極の接触抵抗が低減する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を容易に実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上方に形成されたAlGaN層3と、AlGaN層3上に形成されたAlGaN層4と、AlGaN層4上に形成された電子走行層5と、電子走行層5上方に形成された電子供給層6と、が設けられている。AlGaN層3の組成をAlx1Ga1-x1N、AlGaN層4の組成をAlx2Ga1-x2Nと表すと、「0≦x1<x2≦1」の関係が成り立つ。AlGaN層4の上面には、AlGaN層4の下面に存在する正の電荷よりも多くの負の電荷が存在している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層のクラックをより一層低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基材1と、基材1の上方に形成された初期層2と、初期層2上に形成され、III−V族化合物半導体を含むコア層3と、が設けられている。初期層3として、コア層3に含まれるIII-V族化合物半導体のIII族原子の層が形成されている。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子

【課題】リーク電流が低減された、耐圧性が高い窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子を提供すること。

【解決手段】基板上に少なくともガリウム原子を含むIII族原子と窒素原子とからなる窒化物系化合物半導体層をエピタキシャル成長する成長工程と、素子構造形成前に、前記窒化物系化合物半導体層にレーザ光または電離放射線を照射し、前記窒化物系化合物半導体層中のIII族空孔と水素原子との複合体を分解する分解工程と、を含む。

(もっと読む)

201 - 220 / 1,144

[ Back to top ]