Fターム[5F102GT03]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688) | 高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

Fターム[5F102GT03]に分類される特許

81 - 100 / 912

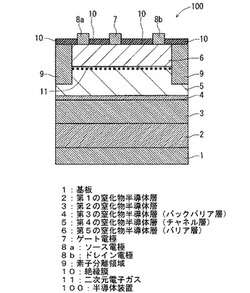

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】窒化サファイア基板をアルカリエッチングし、窒化サファイア基板を清浄化する。その後、III族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

ノーマリオフ型ヘテロ接合電界効果トランジスタ

【課題】p型不純物のドーピングおよびそのp型不純物の活性化を必要とすることなく、簡便かつ低コストでノーマリオフ型HFETを提供する。

【解決手段】ノーマリオフ型HFETは、厚さt1のアンドープAlxGa1−xN層(11)、この層(11)へ電気的に接続されかつ互いに隔てられて形成されたソース電極(21)とドレイン電極(22)、これらソース電極とドレイン電極との間でAlxGa1−xN層上に形成された厚さt2のアンドープAlyGa1−yN層(12)、ソース電極とドレイン電極との間においてAlyGa1−yN層の部分的領域上でメサ型に形成された厚さt3のアンドープAlzGa1−zN層(13)、およびAlzGa1−zN層上に形成されたショットキーバリア型ゲート電極(23)を含み、y>x>zおよびt1>t3>t2の条件を満たすことを特徴としている。

(もっと読む)

エピタキシャル基板

【課題】シリコン基板を下地基板とし、基板サイズに比して問題ない程度に反りが抑制され、半導体素子の作製に好適なエピタキシャル基板を提供する。

【解決手段】エピタキシャル基板10が、シリコン単結晶からなる下地基板1と、下地基板1の上に形成された複数のIII族窒化物層2,3,4からなるIII族窒化物層群と、を備えており、下地基板1が、ボロンが添加されてなることでp型の導電性を有し、かつ、比抵抗が0.01Ω・cm以上0.1Ω・cm以下であり、複数のIII族窒化物層2,3,4がそれぞれ、少なくともAlまたはGaを含み、エピタキシャル基板の反り量をSR(単位:μm)、窒化物層群の総膜厚をte(単位:μm)、下地基板1の膜厚をts(単位:mm)、下地基板1の直径をds(単位:mm)とするときに、規格化反り指数KがK={(SR/te)×(ts/ds)2}≦1×10-3なる関係式をみたすようにする。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

パッケージ

【課題】電流容量が高く、かつ生じる応力が低減されてクラックの発生が抑制され、信頼性の高いパッケージを提供する。

【解決手段】パッケージ外壁16と、パッケージ外壁16を貫通する貫通孔と、貫通孔にはめ込まれた凸状フィードスルー25と、凸状フィードスルー25に固定され端子電極21bとを備え、端子電極21bは、相対的に線熱膨張率は低いが抵抗率が高い第1の金属層90と、相対的に線熱膨張率は高いが抵抗率が低い第2の金属層80a,80bとを備える。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

半導体装置の製造方法及び半導体基板の洗浄方法

【課題】半導体基板の洗浄をより効率的に行うことができる半導体装置の製造方法及び半導体基板の洗浄方法等を提供する。

【解決手段】半導体基板20をその主面を鉛直方向及び水平方向から傾斜させて保持し、酸を含む洗浄液26に半導体基板20を浸漬する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート部におけるリーク電流が低減できる反面、プロセス上の制約があるため製造が困難で、ゲートリーク電流を安定して低減させることが困難だった。

【解決手段】基板と、前記基板上に形成され且つ二次元キャリアガスを有する半導体機能層と、前記半導体機能層上において互いに離間して形成される第1及び第2の主電極と、前記半導体機能層上における前記第1及び第2の主電極間に形成される制御電極と、前記半導体機能層と前記制御電極との間に形成される金属酸化膜と、を備え、

前記金属酸化膜と前記半導体機能層との接合界面における結晶格子は不連続であることを特徴とする半導体装置。

(もっと読む)

パッケージ

【課題】ベース面の反りの少ないパッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートとは異なる材料からなる金属壁16とを備え、導体ベースプレートは、対抗する1対の端面100a・100bが緩やかな弧を有し、金属壁も緩やかな弧を有しているので、接合時や基板実装時、キャップ半田付け時の反りの発生を抑制できる。

(もっと読む)

半導体装置

【課題】III族窒化物半導体を主材料として含むFETにおいて、ゲート−ドレイン間に高電圧を印加した場合でも、素子の劣化が発生し難くし、より信頼度を高くしたFETの提供。

【解決手段】基板上10に、[0001]または[000−1]結晶軸に平行な成長モードにて、格子緩和したバッファ層11、チャネル層12、電子供給層13をこの順にそれぞれIII族窒化物半導体を用いて形成された積層構造にあって、バッファ層11と電子供給層13の内、チャネル層12のIII族原子面側にある層は、チャネル層12のV族原子面側にある層よりもa軸長が大きく、電子供給層13は、チャネル層12よりもバンドギャップが大きい、電界効果トランジスタを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

81 - 100 / 912

[ Back to top ]