Fターム[5F110GG28]の内容

Fターム[5F110GG28]に分類される特許

21 - 40 / 2,818

薄膜トランジスタ、その製造方法、及び表示装置

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】薄膜トランジスタのチャネル層となる酸化物層と絶縁層からなる積層構造であって、

前記酸化物層において、25×25μm2における表面電位の最大値と最小値の電位差が60mV以下であることを特徴とする積層構造。

(もっと読む)

表示装置及び電子機器

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、

温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体

層によって構成されるトランジスタを適用する。なお、当該酸化物半導体層を高純度化す

ることで、当該トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃

におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表

示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上

述したように当該トランジスタは、85℃という高温においてもオフ電流値を100aA

/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置

の表示の劣化を抑制することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。該半導体装置を作製する。半導体装置を歩留まりよく作製し、生産性を向上させる。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程によりゲート電極層、又はソース電極層及びドレイン電極層を形成後、ゲート電極層又は酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の残留物を除去する工程を行う。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタでは、酸化物半導体膜への水素原子の混入が信頼性に悪影響を与える。製造後の半導体装置に混入しうる、水素原子を有する物質として代表的なものは、水である。そこで酸化物半導体を用いた半導体装置に混入する、水素原子を有する物質、特に水を低減することとする。

【解決手段】高密度な酸化窒化シリコン膜は水を含む雰囲気下であっても水の侵入を防ぐ効果が高く、膨潤が少ないことが明らかとなった。そこで高密度な酸化窒化シリコン膜を保護膜として設け、酸化物半導体を用いた半導体装置への水の侵入を防ぐ。具体的には、密度が2.32g/cm3以上、またはプレッシャークッカー試験前後において膨潤率が4体積%以下、またはフーリエ変換型赤外分光法によるスペクトルのピーク(極大吸収波数)が1056cm−1以上に現れる、酸化窒化シリコン膜を保護膜として用いる。

(もっと読む)

酸化物焼結体およびスパッタリングターゲット、並びにその製造方法

【課題】表示装置用酸化物半導体膜の製造に好適に用いられる酸化物焼結体であって、高いキャリア移動度を有する酸化物半導体膜を異常放電や割れを抑制しつつ成膜可能な酸化物焼結体を提供する。

【解決手段】本発明の酸化物焼結体は、酸化亜鉛と;酸化インジウムと;Ti、Mg、Al、およびNbよりなる群から選択される少なくとも1種の金属の酸化物と、を混合および焼結して得られる酸化物焼結体であって、前記酸化物焼結体をX線回折したとき、ZnmIn2O3+m(mは5〜7の整数)相、In2O3、及びZnOの各結晶相を含むと共に、相対密度95%以上、比抵抗0.1Ω・cm以下である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

生体情報評価システム

【課題】顕微鏡で観察するのと同時に生体関連物質の信号情報を透明バイオセンサで取得する場合に、その信号情報を正確に取得することができる生体情報評価システムを提供する。

【解決手段】透明基材とその透明基材上に設けられた薄膜トランジスタ素子部及び透明な生体関連物質感応部とを有し、その薄膜トランジスタ素子部が酸化物半導体膜を有する透明バイオセンサ10と、透明バイオセンサ10が有する生体関連物質感応部に載置される生体関連物質から信号情報を取得する電気信号測定装置101と、透明バイオセンサ10をステージ53上にセットし、透明バイオセンサ10に光源光62,74を照射して生体関連物質感応部に載置される生体関連物質を観察する顕微鏡90とを少なくとも備え、透明バイオセンサ10と光源光62,74との間に紫外線カットフィルタ51を設けた生体情報評価システム50により上記課題を解決した。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させる。

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供することを課題の一とする。また、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。また、暗所でも長時間の利用が可能な、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。

【解決手段】高純度化された酸化物半導体を用いた薄膜トランジスタで回路を構成し、画素が一定の状態(映像信号が書き込まれた状態)を保持することを可能とする。その結果、静止画を表示する場合にも安定した動作が容易になる。また、駆動回路の動作間隔を長くできるため、表示装置の消費電力を低減できる。また、自発光型の表示装置の画素部に蓄光材料を適用し、発光素子の光を蓄えれば、暗所でも長時間の利用が可能になる。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

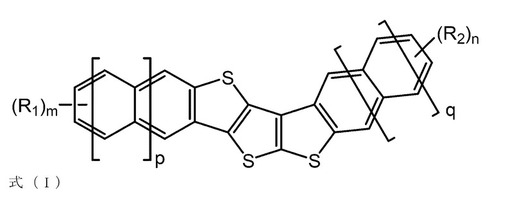

非対称ジベンゾジチエノチオフェン化合物

【課題】高い移動度と、優れた安定性を示す電子機器(例えば、薄膜トランジスタ)のための半導体層に使用できる半導体化合物および該化合物を使用した電子機器の提供。

【解決手段】下記一般式(I)で表される非対称半導体化合物。

(式中、R1およびR2は、それぞれ独立してアルキル、置換アルキル、アルケニル等で、pおよびqは、独立して0または1である。)

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体素子

【課題】酸化物半導体層を用いた半導体素子であって、Vthの変化が抑制された、特性の安定化した半導体素子を提供する。

【解決手段】In(インジウム)およびO(酸素)を含む酸化物半導体層と、Si(珪素)、F(フッ素)およびN(窒素)を含む絶縁層と、を有する半導体素子である。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

半導体装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

21 - 40 / 2,818

[ Back to top ]