Fターム[5F110HK40]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | シリサイド化 (743)

Fターム[5F110HK40]に分類される特許

41 - 60 / 743

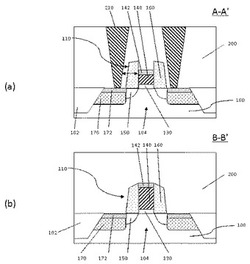

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

MOSトランジスタの製造方法

【課題】 本発明は、メタルソース/ドレインを有するMOSトランジスタにおいて、メタルソース/ドレインの位置制御且つショットキーバリアハイトの制御の両者を実現できる技術を提供することを課題とする。

【解決手段】 SOI層上にゲート電極構造を形成する工程と、該ゲート電極構造をマスクにSOI層上に窒素添加Ni膜を成膜する工程と、窒素添加Ni膜上にTiN膜を形成する工程と、窒素雰囲気中でアニールしSOI層中にMOSトランジスタのソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極構造をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化アニールする工程とを含むMOSトランジスタの製造方法。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

MOSトランジスタの製造方法

【課題】メタルソース/ドレインを有する極薄SOIMOSトランジスタにおいて、ゲート電極/ゲート絶縁膜の側壁につけた保護膜エッジからゲートエッジまでソース/ドレインの位置の制御とショットキーバリアハイトの制御の両者が実現できるMOSトランジスタの製造方法を提供する。

【解決手段】SOI層上にゲート電極を形成する工程と、該ゲート電極の側面にスペーサーを形成する工程と、該ゲート電極及び該保護膜をマスクにSOI層上に窒素添加Ni膜を成膜する工程と該Ni膜上にTiN膜を形成する工程と、窒素中でアニールしSOI層中にソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極及び該保護膜をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化する工程とを含むMOSトランジスタの製造方法。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

フィンを含む半導体構造およびその形成方法

【課題】フィン高さの改良を図れるフィンの形成方法を提供すること。

【解決手段】実施形態のフィン形成の方法は、まず、半導体基板上に多層構造を形成する。前記半導体構造は、前記半導体基板上の第1の層、前記第1の層上の第2の層および前記第2の層上の第3の層を具備する。次に、前記半導体基板および前記半導体構造の複数の部分からなる複数のフィンを形成するために、前記半導体基板の複数の上部および前記半導体構造の複数の部分を除去する。次に、前記第2の層および前記第3の層の酸化速度を前記第1の層よりも酸化速度よりも小さくしながら、前記第1の層を選択的に酸化する。次に、前記選択的な酸化の後に前記複数のフィン間の空隙を絶縁材料で充填する。そして、フィンを露出させるために少なくとも前記絶縁材料の一部をリセスし、前記フィンの少なくとも一つの側面または前記フィンの上面をチャネル領域にする。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

41 - 60 / 743

[ Back to top ]