Fターム[5F110HL14]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | コンタクトホールの形状又は製法に工夫 (361)

Fターム[5F110HL14]に分類される特許

61 - 80 / 361

液晶表示装置および液晶表示装置の製造方法

【課題】液晶表示装置の製造コストの低減を図る。

【解決手段】電界効果型の薄膜トランジスタを備える液晶表示装置であって、薄膜トランジスタの半導体層に、インジウムを材料に含む透明アモルファス酸化物半導体が用いられ、半導体層は、ソース電極およびドレイン電極並びにそれらの電極線として必要な領域を含む形状に形成され、半導体層に積層されるソース・ドレイン層に、インジウムを含む金属薄膜が用いられ、ソース・ドレイン層に積層される絶縁層に、窒化珪素による絶縁膜が用いられ、薄膜トランジスタのチャネル部が、絶縁層とソース・ドレイン層とに設けられた開口部によって形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理及び酸素ドープ処理された酸化物半導体膜を有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

カーボンナノチューブ電界効果トランジスタを含む集積回路、およびその製造方法

【課題】カーボンナノチューブ電界効果トランジスタを含む集積回路であって、その製造プロセスにプラズマ環境下での工程が含まれていても、優れた特性のカーボンナノチューブ電界効果トランジスタを維持する手段を提供する。

【解決手段】1の半導体基板上に配置された、電界効果トランジスタと、MOSトランジスタと、前記電界効果トランジスタと前記MOSトランジスタとを接続するメタル配線と、を含む集積回路であって:前記電界効果トランジスタは、ゲート絶縁膜と、前記ゲート絶縁膜上に形成されたカーボンナノチューブを含むチャネルと、前記カーボンナノチューブを被覆する絶縁保護膜と、前記絶縁保護膜上であって前記チャネルを覆う領域に配置された金属膜と、前記チャネルに接続されたソース電極およびドレイン電極と、前記チャネルを制御可能なゲート電極とを有し、ここで前記メタル配線は、プラズマエッチング法により形成された配線である、集積回路。

(もっと読む)

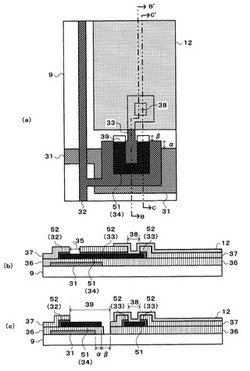

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

表示装置およびその製造方法

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

光電変換装置、エックス線撮像装置及び光電変換装置の製造方法

【課題】外部接続端子の接続信頼性を向上させることができると共に、簡単な工程で製造

できるようにした光電変換装置を提供すること。

【解決手段】本発明の光電変換装置は、フォトダイオード25及びTFT24がマトリク

ス状に配置され、周辺部に複数の外部接続端子が形成され、フォトダイオードは、第1電

極251がTFT24に接続され、第2電極252がバイアス線23に接続され、バイア

ス線23がバイアス線用の外部接続端子に電気的に接続されており、バイアス線23は、

透明導電性金属酸化物で形成され、光電変換装置の光の入射面の全面に亘って形成されて

いると共に、バイアス線用の外部接続端子まで延在されて前記バイアス線用の外部接続端

子の最上部側に配置されている。

(もっと読む)

パターン形成方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等のパターンを作製する方法、さらには、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜、良好なマスクパターン、及びコンタクトホールを形成する方法を提案し、更には低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】本発明の一は、膜上にぬれ性の低い1のマスクパターンを形成した後、第1のマスクパターンを介して、膜上にぬれ性の高い材料を塗布又は吐出して第2のマスクパターンを形成し、第1のマスクパターンを除去して、第2のマスクパターンをマスクとして第1の膜の一部を除去する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】工程を単純化することのできる半透過型薄膜トランジスタの製造方法を提供する。

【解決手段】第1及び第2基板を提供し、第1マスク工程で第1基板上にゲートラインを形成し、第2マスク工程で第1基板上のゲート絶縁膜とゲート絶縁膜上の半導体パターンと半導体パターン上の画素領域を定義するようにゲートラインと交差するデータラインとソース電極及びドレイン電極を形成し、第3マスク工程でデータライン上の有機絶縁膜とソース電極及びドレイン電極を形成し有機絶縁膜を貫通する透過ホールを形成し、第4マスク工程で有機絶縁膜を貫通してドレイン電極と接続された画素電極及び透過ホールを形成し、透過ホールの画素電極を露出させる反射電極を画素電極上に形成する液晶表示装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

液晶表示装置、液晶表示装置用薄膜トランジスタアレイ基板及びその製造方法

【課題】トランジスタ基板に有機膜を設けて性能を高めた液晶表示装置を、より少ない製造工程数により製造することができ、生産性を向上させることができる液晶表示装置用トランジスタ基板及びその製造方法を提供する。

【解決手段】透明絶縁性基板25の上に、ゲート電極26、ゲート絶縁膜27、半導体層19、ソース電極20及びドレイン電極21、パッシベーション膜28が、記載順に積層され、対向基板12との間に液晶層30を充填して対向配置された液晶表示装置用トランジスタ基板において、データ配線18及びドレイン電極21の下の半導体層19と、ソース電極20の下の半導体層19を切り離した。

(もっと読む)

61 - 80 / 361

[ Back to top ]