Fターム[5F110HL14]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | コンタクトホールの形状又は製法に工夫 (361)

Fターム[5F110HL14]に分類される特許

21 - 40 / 361

電気光学装置の製造方法

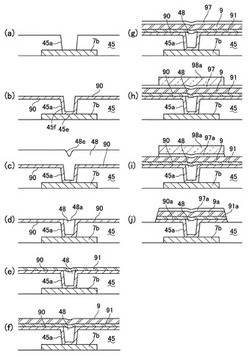

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置をより少ない工程で作製する。

【解決手段】トランジスタと、画素電極とを有し、トランジスタは、第1のゲート電極と、第1のゲート電極上の第1の絶縁層と、第1の絶縁層上の半導体層と、半導体層上の第2の絶縁層と、第2の絶縁層上の第2のゲート電極とを有し、第1のゲート電極は、第1の絶縁層を介して、半導体層と重なる領域を有し、第2のゲート電極は、第2の絶縁層を介して、半導体層と重なる領域を有し、画素電極は、第2の絶縁層上に設けられ、第1の領域は、第2のゲート電極の少なくとも一部が、半導体層の少なくとも一部と重なる領域のうちの、少なくとも一部の領域であり、第2の領域は、画素電極が設けられた領域のうちの、少なくとも一部の領域であり、第1の領域における第2の絶縁層は、第2の領域における第2の絶縁層よりも薄い。

(もっと読む)

表示装置

【課題】画素内に容量の大きな保持容量を有する表示装置を提供する。

【解決手段】表示装置は、第1の電極と第2の電極と、ソース電極とドレイン電極のうちの一方が前記第1の電極と接続された薄膜トランジスタと、前記一方の電極よりも上層に順に形成される第1のシリコン窒化膜および有機絶縁膜とを有する。前記第2の電極は前記有機絶縁膜よりも上層に形成され、第2のシリコン窒化膜は前記第2の電極と前記第1の電極との間の層に形成され、前記第1のシリコン窒化膜と前記第2のシリコン窒化膜は両者を貫通しソース電極とドレイン電極のうち一方の電極と前記第1の電極とを接続するコンタクトホールを有し、前記第2のシリコン窒化膜は、前記一方の電極と接触する領域を持たず、前記第2のシリコン窒化膜の下面が前記コンタクトホールにおいて前記第1のシリコン窒化膜の上面と接触している。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

表示装置、表示装置の製造方法および電子機器

【課題】低コストかつ簡易なプロセスで製造することが可能な表示装置およびその製造方法を提供する。

【解決手段】表示装置1は、酸化物半導体よりなる半導体層12上の選択的な領域(チャネル領域12A)に、ゲート絶縁膜13を介してゲート電極14が設けられ、そのチャネル領域12Aに隣接する領域(ソース・ドレイン接続領域12B)にソース・ドレイン電極層16が電気的に接続される。半導体層12では、これらのチャネル領域12Aおよびソース・ドレイン接続領域12Bとは異なる領域(画素電極部12C)がアノードとして利用される。製造プロセスにおいて、フォトマスク、フォトレジストなどの使用部材を減らし、工程数を削減することができる。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

21 - 40 / 361

[ Back to top ]