Fターム[5F140BA08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | InP (200)

Fターム[5F140BA08]に分類される特許

61 - 80 / 200

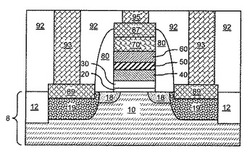

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

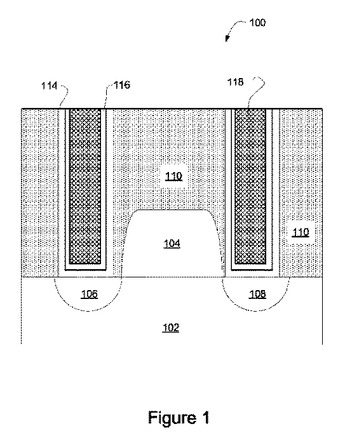

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

改善されたオン/オフ電流比の高移動度多重ゲートトランジスタ

【課題】 金属酸化物半導体(MOS)トランジスタとその形成方法を提供する。

【解決手段】 多重ゲートトランジスタは、基板、第1半導体材料で形成された中央フィン、及び中央フィンの対向側壁上の第1部分と第2部分を含み、第1半導体材料とは異なる第2半導体材料を包含する半導体層を含む基板上の半導体フィン、この半導体フィンの側壁の周囲を包むゲート電極、及び半導体フィンの対向端のソース領域とドレイン領域を含み、中央フィンと半導体層の各々は、ソース領域からドレイン領域に延伸する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体装置の製造方法

【課題】high-kゲート誘電体のパターニングが不要な半導体装置の製造方法を提供する。

【解決手段】第1の領域が第1の厚さに、第2の領域が第1の膜さよりも薄い第2の厚さになるようにゲート誘電体層204を半導体基板202上に形成し、ゲート誘電体層204上にhigh-kの原子の層212を形成し、熱処理を行って、第1の領域に第1の厚さ及び第1の組成のうち少なくとも一方を有するhigh-kゲート誘電体層216を形成し、第2の領域に第1の厚さよりも薄い第2の厚さ及び第2の組成のうち少なくとも一方を有するhigh-kゲート誘電体層218を形成する。

(もっと読む)

High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体

【課題】High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体を提供する。

【解決手段】デバイスを形成する方法は、基板を用意するステップと、基板上に界面層を形成するステップと、界面層上にHigh−k誘電体層を堆積するステップと、High−k誘電体層上に酸素除去層を堆積するステップと、アニールを実施するステップとを含む。High−k金属ゲート・トランジスタは、基板と、基板上の界面層と、界面層上のHigh−k誘電体層と、High−k誘電体層上の酸素除去層とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体の酸化物を安定化させることができる上、欠陥密度が低くて電子移動度が高い誘電体層を得て、デバイスの信頼性及び性能を大幅に改善することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10内に設け、第1のゲルマニウムドープト領域を含む第1の電極と、第1の電極上に設け、半導体酸化物及び安定金属を含む第1の誘電体層23と、第1の誘電体層23上に設ける第2の電極とを備える。第1の電極及び第2の電極によりキャパシタを形成する。

(もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】横方向の寸法の増大を抑制しつつ、横型二重拡散電界効果トランジスタのソースとドレインとの間の電界を緩和する。

【解決手段】N型ドリフト層17には、埋込絶縁層14下に配置されたP−ダンパ層19を形成するとともに、P−ダンパ層19を取り囲むように配置されたN−ダンパ層18を形成し、N−ダンパ層18およびP−ダンパ層19にて埋込絶縁層14下が空乏化されるように不純物濃度を設定する。

(もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

非シリコンチャネルMOSデバイス中のフェルミレベルピンニングの低減方法

【課題】金属酸化物半導体(MOS)デバイス中の、GeやIII−V化合物(例えばGaAsまたはInGaAs)のような高移動度半導体化合物チャネル中の、フェルミレベルピンニング(FLP)を低減(回避)する方法の提供。

【解決手段】半導体化合物11上のゲート誘電体19上にゲート電極20を形成し、水素アニール21を実施する。水素はゲート電極のPtやPdのような貴金属による触媒作用により原子状水素を形成しアニールを行い半導体化合物11とゲート誘電体19との界面を界面をパッシベートし、更には欠陥を回復する。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】面積を増大させることなく、過電圧に対する耐性を高めることを課題の一つとする。

【解決手段】第1の端子部100に設けられ、第1のn型不純物領域106と、平面視において前記第1のn型不純物領域106の内周部に設けられた第1の抵抗領域107と、平面視において前記第1の抵抗領域107の内周部に設けられた第1のp型不純物領域108と、を有する第1の半導体領域103と、前記第2の端子部101に設けられ、第2のp型不純物領域109と、平面視において前記第2のp型不純物領域109の内周部に設けられた第2の抵抗領域110と、前記第2の抵抗領域110の内周部に設けられた第2のn型不純物領域111と、を有する第2の半導体領域104と、有する構成である。

(もっと読む)

61 - 80 / 200

[ Back to top ]