Fターム[5F140BA08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | InP (200)

Fターム[5F140BA08]に分類される特許

101 - 120 / 200

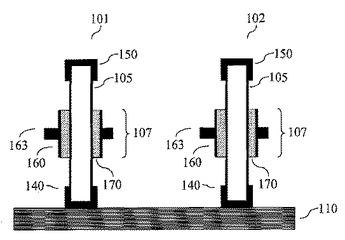

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

絶縁膜の作製方法及び半導体装置の作製方法

【課題】非感光性のシロキサン樹脂を用いて、ウェットエッチング法で所望の形状に形成された絶縁膜を形成することができる、絶縁膜の作製方法を提供する。

【解決手段】有機溶媒中にシロキサン樹脂またはシロキサン系材料を有する懸濁液を用いて薄膜を形成し、薄膜に第1の加熱処理を施し、第1の加熱処理後の薄膜上にマスクを形成し、有機溶媒を用いてウェットエッチングすることで、第1の加熱処理後の薄膜の形状を加工し、加工された薄膜に第2の加熱処理を施す。

(もっと読む)

ゲート・フィン間の重なりセンシティビティが低減されたFinFET

【課題】 均一な幅の短いフィンを有するFinFETを形成する改善された方法を提供すること。

【解決手段】 本発明の実施形態は、フィン型電界効果トランジスタ(FinFET)における比較的均一な幅のフィン、並びに、これを形成するための装置及び方法を提供するものである。フィン構造体は、該フィン構造体の側壁部分の表面が、第1の結晶方向に対して垂直になるように形成することができる。フィン構造体の端部のテーパ状領域は、第2の結晶方向に対して垂直であり得る。フィン構造体に結晶依存エッチングを行うことができる。結晶依存エッチングは、第2の結晶方向に対して垂直なフィンの部分から、相対的により速く材料を除去することができ、これにより、比較的均一な幅のフィン構造体がもたらされる。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】化合物半導体領域の表面における化学的な安定性の向上と、絶縁膜自体の良好な絶縁性という、保護絶縁膜に求められる相反する要求を共に満たし、高性能で信頼性に優れた半導体装置を実現する。

【解決手段】化合物半導体領域2の表面を覆う保護絶縁膜10を性質の異なる第1の絶縁膜11と第2の絶縁膜12との2層構造を有するように形成する。第1の絶縁膜11は非ストイキオメトリのシリコン窒化膜、第2の絶縁膜12はほぼストイキオメトリの状態とされたシリコン窒化膜とする。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されても良好な品質を有するゲート絶縁膜を備え、信頼性が高く、高速に動作可能な半導体装置およびその製造方法を提供する。

【構成】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成されたゲート絶縁膜1006と、上部におけるLaの濃度がその他の部分のLaの濃度よりも大きい第1の電極形成膜1015を含む第1のゲート電極とを有するp型MISFETとを備えている。さらに、n型活性領域1004の上面に形成されたゲート絶縁膜1006と、上部におけるAlの濃度がその他の部分のAlの濃度よりも大きい第2の電極形成膜1014を含む第2のゲート電極とを有するn型MISFETとを備えている。

(もっと読む)

ゲートの誘電性スタックの制御された形成方法

【課題】ゲートの誘電性スタックの制御された形成方法を提供する。

【解決手段】半導体基板に誘電性材料層を形成し、上記誘電性材料層上に希土類酸化物層を堆積し、上記希土類酸化物層上に金属ゲート電極材料を堆積した後、焼き鈍しを行い希土類ケイ酸塩層を形成する。ここで、金属ゲート電極材料を堆積する前に、焼き鈍し工程は行わない。

(もっと読む)

電子デバイスおよびその製造プロセス

【課題】金属酸化物半導体電界効果トランジスタのような金属絶縁体デバイスおよび/または金属絶縁体金属キャパシタを提供する。

【解決手段】装置は、

炭化タンタル、炭窒化タンタル、炭化ハフニウム、および炭窒化ハフニウムからなる組から選択される金属化合物を含む電極と、

窒素とシリコンを含む酸化ハフニウムからなるhigh−k誘電体層であって、少なくとも4.0のk値を有するhigh−k誘電体層と、

電極とhigh−k誘電体層との間に配置された窒素および/またはシリコンおよび/または炭素のバリア層とを含み、

窒素および/またはシリコンおよび/または炭素のバリア層は、1またはそれ以上の金属酸化物を含み、金属酸化物の金属はランタニド、アルミニウム、およびハフニウムからなる組から選択される。

(もっと読む)

電界効果トランジスタ素子およびその製造方法

【課題】改善した能力を備えた、MOSFETやHEMTなどの半導体トランジスタ素子を提供する。

【解決手段】本発明に係る半導体トランジスタ素子は、トランジスタがオンしたとき、電流をトランジスタに通すために、キャリアが移動できるチャネル層を含むチャネルエリア(1)と、チャネル層に対して電流を供給するために、チャネル層と接触したソースエリア(4)およびドレインエリア(5)と、ゲート電極(3)とを備え、好ましくは、ゲート電極とチャネル層との間にゲート誘電体(2)が設けられ、前記チャネル層はIII−V族材料からなり、前記ソースエリアおよびドレインエリアはSiGe(SixGe1−x、xは0と100%の間)を含み、ヘテロ接合(30,31)がIII−V族材料とSiGeの間に存在し、前記ヘテロ接合は、前記電流が前記ヘテロ接合を通過するように配置されており、前記ヘテロ接合(30,31)は、前記ゲート誘電体(2)または前記ゲート電極と交差するように配向している。

(もっと読む)

半導体装置の製造方法およびそれにより得られた半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】本発明は、半導体材料と金属の合金から形成され、合金の仕事関数を変調させる仕事関数変調元素を含む完全にシリサイド化されたゲート電極(4)と、完全にシリサイド化されたゲート電極(4)に接触した誘電体(3)とを含む半導体装置(1)を提供する。完全にシリサイド化された電極と直接接触する誘電体(3)の少なくとも一部は、仕事関数変調元素が誘電体(3)中に注入され、および/または誘電体(3)に向かって拡散するのを実質的に防止するストップ金属を含む。本発明は、また、そのような半導体装置(1)を形成する方法を提供する。

(もっと読む)

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

立体的形状の活性領域を含むCMOS構造体

【課題】 複数の結晶方位の半導体基板領域を有するCMOSデバイス及びCMOS構造体、及び、そのようなCMOSデバイス及びCMOS構造体を製造するための方法を提供する。

【解決手段】 CMOS構造体は、半導体基板内の第1の活性領域を用いて配置された第1のデバイスを含み、第1の活性領域は、平坦であり、第1の結晶方位を有する。CMOS構造体はまた、半導体基板内の第2の活性領域を用いて配置された第2のデバイスを含み、第2の活性領域は、立体的形状であり、第1の結晶方位の存在しない第2の結晶方位をもつ。第1の結晶方位及び第2の結晶方位は、典型的には電荷キャリア移動度に関して、第1のデバイス及び第2のデバイスの性能を最適化することを可能にする。立体的形状の第2の活性領域はまた、単一厚さを有する。CMOS構造体は、立体的形状の第2の活性領域を形成するための結晶学的特異性エッチャントを用いて製造することができる。

(もっと読む)

絶縁ゲート電界効果トランジスタ

【課題】ノーマリオフ動作が可能な絶縁ゲート電界効果トランジスタを提供する。

【解決手段】このヘテロ接合電界効果トランジスタ(MISHFET)は、AlGaNバリア層104の上にソースオーミック電極105とドレインオーミック電極106が形成されている。AlGaNバリア層104上にSiNxゲート絶縁膜108、p型多結晶SiC層109、オーミック電極であるPt/Auゲート電極110が順次形成されている。p型多結晶SiC層109は仕事関数が相対的に大きいので、ゼロバイアス状態でもMISHFETのチャネルが空乏化されて、ノーマリオフ動作が生じる。

(もっと読む)

半導体デバイス層からの不純物の除去

本発明は、半導体デバイス(1)の製造中に、少なくとも一つの半導体デバイス層(4)から該半導体デバイス層(4)を用いて不純物を除去する方法を提供し、上記少なくとも一つの半導体デバイス層(4)は、化合物半導体材料及び/又はゲルマニウムを備え、少なくとも一つの半導体デバイス層(4)を準備した後、半導体デバイス(1)の製造中に実行される各加熱工程は、900℃以下の温度で、5分以下の時間により決定される低サーマルバジェットを有する。上記方法は、半導体デバイス層(4)よりも不純物に関して高い溶解度を有するゲルマニウム・ゲッタリング層(3)を設けることを備え、ゲルマニウム・ゲッタリング層(3)は、少なくとも一つの半導体デバイス層(4)に直接又は間接に接触して少なくとも部分的に設けられ、これにより、不純物は、少なくとも一つの半導体デバイス層(4)からゲルマニウム・ゲッタリング層(3)へ拡散することができる。本発明は、また、発明の実施態様による不純物の除去方法を用いて半導体デバイスを形成する方法を提供し、及びそれにて得られる半導体デバイスを提供する。  (もっと読む)

(もっと読む)

半導体装置の接合形成方法およびそれにより作製された半導体装置

【課題】半導体装置の所望のソース/ドレイン接合深さの近傍にある、エンドオブレンジ(EOR)領域の存在の、負の影響を低減する。

【解決手段】装置とその装置の製造方法が記載され、それにより、装置がエンドオブレンジ欠陥から離れた浅い接合深さを有する。方法は、シリコンのような結晶半導体中に、第1深さまで、アモルファス領域を形成する工程と、これに続いて、例えば炭素のような置換型元素を、第1深さより浅い深さまで注入する工程とを含む。続いて領域は例えばリンやボロンのような適当なドーパントでドープされ、熱処理工程によりアモルファス領域が再結晶化される。

(もっと読む)

誘電層に適合可能な活性領域

活性領域と、適合可能な誘電層を有する半導体構造を形成する方法を開示する。1つの実施形態においては、半導体構造は、第1の半導体材料の酸化物を含む誘電層を有しており、誘電層と第1の半導体材料との間に第2の(組成的に異なった)半導体材料が形成される。別の実施形態においては、第2の半導体材料の格子構造に一軸性ひずみを与える目的で、第2の半導体材料の一部は、第3の半導体材料に置き換えられる。 (もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

垂直型電界効果トランジスタ・アレイ及びその製造方法

【課題】 性能が向上した垂直型電界効果トランジスタ・アレイを提供すること。

【解決手段】 垂直型電界効果トランジスタの半導体構造体、及び垂直型電界効果トランジスタの半導体構造体を製造する方法が、半導体ピラーのアレイを提供する。半導体ピラー・アレイ内の各半導体ピラーの各垂直部分は、隣接する半導体ピラーまでの分離距離より広い線幅を有する。代替的に、アレイは、随意的に上記の線幅及び分離距離の制限の中で、異なる線幅を有する半導体ピラーを含むことができる。半導体ピラーのアレイを製造する方法は、エッチング・マスクとして用いられる前に少なくとも1つのスペーサ層が環状に増大される、フォトリソグラフィを用いて最小寸法に作られたピラー・マスク層を用いる。

(もっと読む)

簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体

【課題】 簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体を提供すること。

【解決手段】 ゲート誘電体の下にあるチャネル領域内の応力を強化するために、新しいデュアル応力ライナ構成が用いられる、完全にシリサイド化されたゲート電極を有するnFETを含む半導体構造体が提供される。新しいデュアル応力ライナ構成は、nFETの完全にシリサイド化されたゲート電極の上面と実質的に同一平面にある上面を有する第1の応力ライナを含む。本発明によると、第1の応力ライナは、完全にシリサイド化されたゲート電極を含むnFETの上には存在しない。代わりに、本発明の第1の応力ライナは、完全にシリサイド化されたゲート電極を有するnFETを部分的に包み込む、すなわちその両側を囲む。第1の応力ライナのものと反対の極性を有する(すなわち、反対の応力型の)第2の応力ライナが、第1の応力ライナの上面上及び完全にシリサイド化されたFETを含むnFETの上に配置される。本発明によると、第1の応力ライナは引張応力ライナであり、第2の応力ライナは圧縮応力ライナである。

(もっと読む)

101 - 120 / 200

[ Back to top ]