Fターム[5F140BA08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | InP (200)

Fターム[5F140BA08]に分類される特許

21 - 40 / 200

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体記憶装置

【課題】GIDLによるホールの発生効率を向上させることが可能な半導体記憶装置を提供する。

【解決手段】フィン3の両側にゲート絶縁膜5を介して設けられ、フィン3にチャネル領域を形成するゲート電極Gと、チャネル領域間のボディ領域にホールを閉じ込めるポテンシャルバリアを形成する不純物拡散層6と、チャネル領域を挟み込むようにしてフィン3に形成されたソース層S/ドレイン層Dとを備え、データ‘1’が書き込まれる際にゲート電圧が負電位かつ基板バイアス電圧およびドレイン電圧が正電位に設定される。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

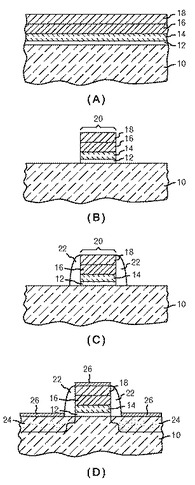

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

半導体結合超伝導三端子素子

【課題】超伝導電極層としてMgB2、接合部にInGaAsチャネル層を用い、第三電極を用いて超伝導電流を制御する半導体結合超伝導三端子素子において、超伝導電極層の成長時のMgのInGaAsチャネル層への拡散を抑制し、接合特性を改善した半導体結合超伝導三端子素子を提供することにある。

【解決手段】超伝導電流のチャネル層となるInGaAs層とソース電極となる第1のMgB2超伝導電極層及びドレイン電極となる第2のMgB2超伝導電極層とその二つの超伝導電極間のInGaAs層中に流れる超伝導電流を制御する第三電極とを有する半導体結合超伝導三端子素子において、MgB2超伝導電極層1,2とInGaAsチャネル層6との層間にAu層6が挿入された。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

21 - 40 / 200

[ Back to top ]