Fターム[5F140BA08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | InP (200)

Fターム[5F140BA08]に分類される特許

41 - 60 / 200

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

量子井戸型半導体装置

量子井戸型半導体装置、および量子井戸型半導体装置を形成する方法について示した。本方法は、基板の上部に配置され、量子井戸チャネル領域を有するヘテロ構造を提供するステップを有する。また、この方法は、ソースおよびドレイン材料領域を形成するステップを有する。また、この方法は、ソースおよびドレイン材料領域に溝を形成するステップを有し、ドレイン領域から分離されたソース領域が提供される。また、この方法は、溝内のソース領域とドレイン領域の間に、ゲート誘電体層を形成するステップと、溝内のゲート誘電体層の上部に、ゲート電極を形成するステップとを有する。  (もっと読む)

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

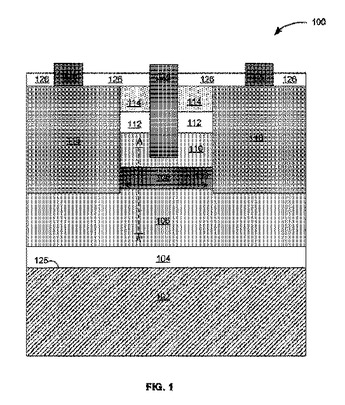

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体デバイス及びその製造方法

【課題】従来よりも界面準位密度を低減させることができる半導体デバイス及びその製造方法を提供する。

【解決手段】窒素ガス雰囲気下で低ダメージなECRプラズマを用いたECRプラズマ処理を行うことにより、III−V族化合物半導体層2の表面を窒化処理したことで、当該III−V族化合物半導体層2にIn−N結合及びGa−N結合を形成しAs酸化物を抑制して界面特性を向上させることができ、かくして従来よりも界面準位密度が低減されたMOSFET1を提供できる。また、アニール処理することにより、窒化処理層5においてGa−N結合が支配的となった界面結合状態を形成し、界面準位密度を一段と低減させることができる。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

集積回路構造及びその製造方法

【課題】 非対称的なソース及びドレイン領域を有する構造を提供する。

【解決手段】 本発明の方法は、少なくとも1つの半導体チャネル領域を有する基板と、半導体チャネル領域を覆うように基板の上面に設けられたゲート誘電体層と、ゲート誘電体層上のゲート導電体とを有する構造を形成する。非対称的な側壁スペーサがゲート導電体の側壁に配置され、そして非対称的なソース及びドレイン領域が半導体チャネル領域に隣接して基板内に配置される。ソース及びドレイン領域の一方は、他方よりもゲート導電体の中心に近づけられる。ソース及びドレイン領域は、半導体チャネル領域に物理的な応力を与える材料で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

高移動度マルチゲートトランジスタのフィン構造

【課題】 半導体トランジスタの垂直フィン構造及びその製造方法を提供する。

【解決手段】 半導体トランジスタの垂直フィン構造であって、半導体基板、この半導体基板の上部のフィン層、及びこのフィン層を覆うキャッピング層を含み、半導体基板は、IV族半導体材料を含み、フィン層は、IV族半導体材料を含み、キャッピング層は、III−V族半導体化合物を含み、フィン層は、半導体トランジスタのチャネルとなり、キャッピング層は、フィン層に歪みを加え、チャネルを通過する移動度を向上させる垂直フィン構造。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

41 - 60 / 200

[ Back to top ]