Fターム[5F140BA08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 3−5族 (1,737) | InP (200)

Fターム[5F140BA08]に分類される特許

181 - 200 / 200

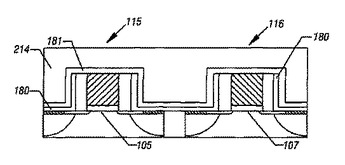

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【課題】 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【解決手段】 ゲート積層体(29)と、ゲート積層体(29)の側壁上に配置される1対の第1のスペーサ(32)と、ゲート積層体(29)の両側に配置され、それから第1の間隔を置かれる1対の半導体合金領域(39)とを含む電界効果トランジスタ(FET)(10)が提供される。FET(10)のソース及びドレイン領域(24)は少なくとも部分的に半導体合金領域(39)内に配置され、1対の第1のスペーサ(32)の対応するスペーサによってゲート積層体(29)から、第1の間隔とは異なり得る第2の間隔を置かれる。FET(10)はまた、第1のスペーサ(32)の上に配置される第2のスペーサ(34)と、少なくとも部分的に半導体合金領域(39)の上に重なるシリサイド領域(40)とを含むことができるが、ここでシリサイド領域(40)は第1及び第2のスペーサ(32、34)によってゲート積層体(29)から間隔を置かれる。

(もっと読む)

半導体素子及びその製造方法

【課題】 チャネル領域内のキャリア制御性が優れると共にリーク電流が少ない半導体素子及びその製造方法を提供する。

【解決手段】 基板1上に、エピタキシャル成長により、基板1の表面に対して垂直な方向を含む断面が下底よりも上底が短い台形形状である低濃度ドープダイヤモンド層4を形成する。次に、低濃度ドープダイヤモンド層4の両側に、エピタキシャル成長により低濃度ドープダイヤモンド層4よりも不純物濃度が高い高濃度ドープダイヤモンド層7a及び7bを形成する。そして、高濃度ドープダイヤモンド層7a及び7b上に、金属電極8a及び8bを形成した後、酸化シリコン絶縁層9a及び9bを形成し、更に、低濃度ドープダイヤモンド層4の上に酸化アルミニウム絶縁層10を介してゲート電極11を形成して、高濃度ドープダイヤモンド層7a及び7b間の距離が基板1から遠ざかるに従い短くなる半導体素子とする。

(もっと読む)

半導体素子の製造方法

【課題】エピタキシャル成長法により半導体層を形成する際の加工寸法誤差を少なくすることができる半導体素子の製造方法を提供する。

【解決手段】有機金属化合物を含有する感光性ペーストを塗布した後ベークして、基板1上に感光性マスク層を形成する。この感光性マスク層をフォトリソグラフィによりパターニングし、更に酸化処理又は還元処理して、基板1上に金属酸化物を主成分とするエピタキシャルマスク4を形成する。そして、基板1表面のエピタキシャルマスク4が形成されていない領域上にダイヤモンドをエピタキシャル成長させて、半導体ダイヤモンド層5a及び5bを形成する。エピタキシャルマスク4を除去した後、半導体ダイヤモンド層5a及び5b上に夫々ソース電極7及びドレイン電極8を形成すると共に、基板1表面におけるチャネル領域上にゲート絶縁膜6を介してゲート電極9を形成する。

(もっと読む)

分離ウェルを用いるMOSバラクタ

【課題】 向上した調節能力と高い品質係数Qとを有するバラクタ及びその製造方法を提供すること。

【解決手段】 本発明は、向上した調節能力と高い品質係数Qとを有するバラクタ22、及び、バラクタ22を製造する方法を提供する。本発明の方法は、従来のCMOS処理スキーム又はBiCMOS処理スキームに組み込むことができる。この方法は、第1の導電型の半導体基板12と、該基板12の上部領域11の下方に配置された、第2の導電型のサブコレクタ14又は分離ウェル(すなわち、ドープ領域)とを含む構造体であって、該第1の導電型は、第2の導電型とは異なる構造体を準備するステップを含む。次に、複数の分離領域16が、基板12の上部領域11内に形成され、次いで、ウェル領域が、基板12の上部領域11内に形成される。場合によっては、本発明のプロセスのこの時点で、ドープ領域14が形成される。ウェル領域は、第2の導電型の外側ウェル領域20A及び20Cと、第1の導電型の内側ウェル領域20Bとを含む。ウェル領域の各々のウェルは、分離領域16によって上面で分離される。次に、内側ウェル領域20Bの上方に、少なくとも第1の導電型のゲート導体26を有する電界効果トランジスタが形成される。

(もっと読む)

高k誘電材料と一緒に使用するための界面層

シリコン基板(11)上に純粋なゲルマニウムの層(12)を堆積することができる方法及び装置。このゲルマニウム層は、非常に薄く、約14Åのオーダーであり、シリコン上の純粋なゲルマニウムに関する臨界厚さよりも小さい。該ゲルマニウム層(12)は、シリコン基板(11)と高kゲート層(13)との間の中間層として役立ち、該高kゲート層(13)はゲルマニウム層(12)の上に堆積される。ゲルマニウム層(12)は、高k材料の適用中、酸化物界面層の発生を避けるのに役立つ。半導体構造におけるゲルマニウム中間層の適用は、酸化物不純物のための直列キャパシタンスの不利益無しで機能的な高kゲートを生じさせる。ゲルマニウム層(12)は更に移動度を改善する。  (もっと読む)

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 従来よりも高い温度でも動作できるクーロンブロケードを用いた量子効果素子

を提供すること。

【解決手段】 後方障壁閉じ込めポテンシャルを形成するための下部SiO2層43と上

部SiO2層45と、p−型層47と、これらSiO2層43、45、p−型層47各端

と交わる傾斜面51と、傾斜面51上にSiO2活性層61を介して設けられたゲート電

極31を有し、このゲート電極31のうち、SiO2層43、45の各端を覆うる部分は

狭くなっている。

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

平滑基板上への高K誘電体層の形成

平坦シリコン基板上に、バッファ層と高K金属酸化物誘電体が形成される。基板の平坦度は、高K金属酸化物ゲート誘電体が柱状成長することにより低下する。基板表面は、成膜の前に、水酸基終端で飽和化される。  (もっと読む)

(もっと読む)

MOS電界効果トランジスタ型量子ドット発光素子および受光素子、これらを利用した光電子集積チップおよびデータ処理装置

【課題】 MOS電界効果トランジスタ型量子ドット発光素子および受光素子の提供、MOS電界効果トランジスタ型量子ドット発光素子の製造方法の提供、かかる受発光素子を利用した光電子集積チップ、データ処理装置を提供することを目的とする。

【解決手段】 MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたトンネルSiO2層と、該トンネルSiO2層上に形成されたSi殻内にGe核を内包した量子ドットと、該量子ドット上及び前記トンネルSiO2層上に形成されたコントロールSiO2層と、該コントロールSiO2層上に形成されたゲート電極層と、を有する。MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたゲートSiO2層と、該ゲートSiO2層上に形成されたドープSi層、Ge層及びドープSi層を順次積層してなる積層ゲート電極層と、を有する。

(もっと読む)

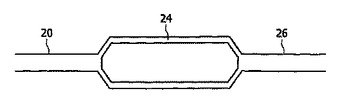

ナノスケールFET

トランジスタデバイスは、ソース領域、ドレイン領域、およびソース領域とドレイン領域の間のチャネル領域を有する連続リニアナノ構造体で形成される。ソース領域(20)とドレイン領域(26)はナノワイヤで形成され、チャネル領域(24)はナノチューブの形である。ソース領域とドレイン領域の間のチャネル領域における伝導を制御するためにチャネル領域(24)に隣接する絶縁ゲート(32)が提供される。  (もっと読む)

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

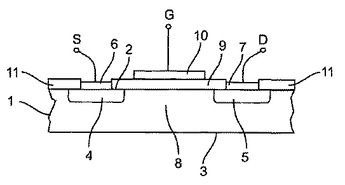

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

半導体デバイス並びに量子井戸構造体を製造する方法及び量子井戸構造体を有する半導体デバイス

量子井戸構造体(4)を備える多重層構造体(3)を基板(2)上に得るための半導体デバイス(1)及び方法が開示されている。量子井戸構造体(4)は、絶縁物質(6、6’)によって挟まれる半導体層(5)を有し、絶縁物質(6、6’)の物質は好ましくは、高誘電率を有する。FETにおいて、量子井戸(4、9)はチャネルとして機能し、より高い駆動電流及びより低いオフ電流が可能になる。短チャネル効果が低減される。多重チャネルFETは、サブ35nmゲート長に対してさえも動作するのに適している。本方法において、量子井戸は、好ましくはMBEを用いて、半導体物質及び高誘電率物質のエピタキシャル成長によって互いの上に交互に形成される。

(もっと読む)

(もっと読む)

181 - 200 / 200

[ Back to top ]