Fターム[5F140BF07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467) | 金属 (3,194) | 高融点金属 (636)

Fターム[5F140BF07]に分類される特許

101 - 120 / 636

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの新規な閾値電圧制御技術を提供する。

【解決手段】半導体装置の製造方法は、半導体基板のp型領域上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、化学量論組成よりも酸素量の少ない酸化アルミニウム膜を形成する工程と、酸化アルミニウム膜上に、タンタルと窒素とを含むタンタル窒素含有膜を形成する工程と、タンタル窒素含有膜上に、導電膜を形成する工程と、導電膜をパターニングして、ゲート電極を形成する工程と、ゲート電極をマスクとして、p型領域にn型不純物を注入する工程と、タンタル窒素含有膜の形成後に、熱処理を行う工程とを有する。

(もっと読む)

電界効果トランジスタの製造方法

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】キャップ層105の表面を塩酸からなる処理液で処理する。処理液は、例えば、塩化水素の37質量%水溶液を、水で5倍(体積)に希釈したものである。次に、基板101を処理液中より引き上げ、直ちにキャップ層105の表面に付着している塩酸を除去する。この塩酸の除去では、水を用いることなく、例えば、キャップ層105の表面に窒素ガスを吹き付けることで付着している塩酸を除去する。

(もっと読む)

電界効果トランジスタ

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】第1障壁層102に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第1不純物導入領域110と、第2障壁層104に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第2不純物導入領域111とを備える。また、第1不純物導入領域110および第2不純物導入領域111は、チャネル層103の電子に不純物散乱を生じさせない範囲でチャネル層103より離間して形成されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】窒化処理によって低下した閾値電圧を、向上させることができる炭化珪素半導体装置の製造方法を提供する。

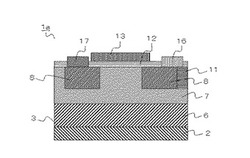

【解決手段】ベース領域7およびソース領域8を含む炭化珪素ドリフト層6上に二酸化珪素を主成分とするゲート絶縁膜11が形成された炭化珪素基板2を窒化処理する窒化処理工程と、窒化処理工程後、炭化珪素基板2を、一酸化二窒素を含む雰囲気中で600℃以上1000℃以下の温度で熱処理する熱処理工程と、を備える。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素MOSFETにおいて、炭化珪素層とゲート絶縁膜との界面に発生する界面準位を十分に低減できず、キャリアの移動度が低下する場合があった。

【解決手段】この発明に係る炭化珪素半導体装置は、炭化珪素層を有し炭化珪素層上にゲート絶縁膜を形成した基板を炉の中に導入する基板導入工程と、基板を導入した炉を加熱して一酸化窒素と窒素とを導入する加熱工程とを備え、加熱工程は、窒素を反応させてゲート絶縁膜と炭化珪素層との界面を窒化する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

多孔性絶縁体及び電界効果トランジスタ

【課題】例えば、チタン酸ストロンチウムを活性層とした電界効果トランジスタのゲート絶縁体としても使用することのできる、新規な絶縁体を提供することを目的とする。

【解決手段】絶縁性を示す材質中に直径5〜100nmである空孔を複数有し、全体の体積に対する前記空孔の占める体積の割合である空孔率が20体積%以上であり、前記空孔には水分が含まれ、前記空孔の体積に対する前記水分の占める体積の割合である水分占有率が23〜100体積%である多孔性絶縁体を使用する。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】CMOS回路の閾値を簡易なプロセスで効率よく制御して、信頼性の高い半導体装置を作製する。

【解決手段】下地ゲート絶縁膜を形成し、下地ゲート絶縁膜上に選択的にマスク膜を形成し、下地ゲート絶縁膜、及び、マスク膜上に第1の金属元素を含む第1のキャップ膜を形成し、nMOSトランジスタ領域の下地ゲート絶縁膜に第1の金属元素を拡散させ、マスク膜、及び、第1のキャップ膜を選択的に除去し、第1の金属元素が拡散したnMOSトランジスタ領域の下地ゲート絶縁膜、及び、pMOSトランジスタ領域の下地ゲート絶縁膜上に第2の金属元素を含む第2のキャップ膜を形成し、下地ゲート絶縁膜に第2の金属元素を拡散させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】トランジスタのランダムバラツキを改善し、トランジスタ特性を所望の値に制御する。

【解決手段】N型MOSFETは、チャネル領域10とエクステンション領域16とハロー領域17とゲート絶縁膜13とゲート電極12とを具備する。チャネル領域10は、半導体基板の表層に形成される。エクステンション領域16は、半導体基板の表層に形成され、チャネル領域10の両端に形成される。ハロー領域17は、エクステンション領域16の下方に形成される。ゲート絶縁膜13は、チャネル領域10上に形成され、High−k材料が添加される。ゲート電極12は、ゲート絶縁膜13上に形成される。チャネル領域10又はハロー領域16に炭素が注入される。High−k材料の添加量は、炭素の注入による閾値電圧の低下量を、High−k材料をゲート絶縁膜13に添加することによる閾値電圧の上昇量により補うことができる添加量である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

101 - 120 / 636

[ Back to top ]