Fターム[5F140BG40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | 研磨、CMP (298)

Fターム[5F140BG40]に分類される特許

101 - 120 / 298

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間の分離領域を含むゲート電極の端部形状の加工が容易となる構造を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の表面よりも高い上面を有する素子分離絶縁膜11により半導体基板に第1及び第2チャネル形成領域を有する第1及び第2半導体領域(12,13)がそれぞれ区分され、第1及び第2チャネル形成領域上にゲート絶縁膜14と第1及び第2ゲート電極(G1,G2)が形成され、その両側部における第1及び第2半導体領域の表層部にソースドレイン領域が形成され、第1及び第2ゲート電極は、第1及び第2半導体領域内において素子分離絶縁膜と略同じ高さを有し、その端部が素子分離絶縁膜の側面に接するように形成された第1導電層15pと、上記端部から素子分離絶縁膜上にはみ出すように第1導電層上に形成された第2導電層16sとを有する構成とする。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の注入量及びチャネル領域中の不純物濃度を容易に制御する。動作特性に優れたFin型電界効果型トランジスタを備えた半導体装置を提供する。

【解決手段】Fin状の半導体基板の部分に犠牲酸化膜を形成した後、マスクパターンをマスクに用いて半導体基板に不純物を注入する。この後、犠牲酸化膜を除去して、半導体基板を露出させた後、露出した半導体基板上にゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置の構造および製造方法

【課題】STI領域の絶縁膜掘り下げにより形成される幅30nm以下の拡散層が配されているFinFETにおいて、寄生抵抗を低減した構造及びその製造方法を提供する。

【解決手段】STI領域105に挟まれ、素子分離領域上方に突き出た幅30nm以下の半導体層にソース及びドレイン領域となる拡散層104が形成されており、ソース及びドレイン領域間のチャネル領域を跨ぐゲート電極を有する凸型Fin構造の電界効果トランジスタであって、前記ソース及びドレイン領域となる拡散層側壁にサイドウォール110b、該サイドウォールに挟まれた拡散層上面に選択エピタキシャル成長シリコン層111、及び該選択エピタキシャル成長シリコン層に接続されるコンタクトプラグ115を有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡便な方法で{111}結晶面にトランジスタを形成することが可能な半導体装置を提供する。

【解決手段】 表面が{100}結晶面で構成されたシリコンを有する基板(20)に、活性領域を画定する素子分離絶縁膜(21)が形成されている。この基板に、少なくとも側面の一部が、{111}結晶面が表れた第1の斜面で構成された凹部(36)が形成されている。第1の斜面上に、第1のトランジスタ(TL1)が形成されている。第1のトランジスタは、第1のゲート電極(41b)、第1のソース、及び第1のドレインを有する。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12にトレンチ14を形成する。トレンチ14において、底部及びその近傍には、角部12A,12Bで丸みを帯びて均一に厚いシリコン酸化膜15Aが形成される。一方、トレンチ14の側壁の上方には、シリコン酸化膜15Aよりも薄く、角部12C,12Dで丸みを帯びたシリコン酸化膜15Bが形成される。さらに、トレンチ14内から外側に延びるゲート電極18が形成される。厚いシリコン酸化膜15Aによりゲート容量が低減され、その上方の薄いシリコン酸化膜15Bにより優れたトランジスタ特性が確保される。また、角部12A,12Bの丸みにより、結晶欠陥が発生しにくくなると共に、ゲート電界が分散されてゲート耐圧が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】高速高周波動作に適した信頼性の高い半導体装置を得ること。

【解決手段】シリコン基板11の表面層に拡張ドレイン領域12とウェル領域13を形成し、拡張ドレイン領域12上に絶縁層20を形成する。その絶縁層20の側壁に犠牲スペーサー領域を形成し、犠牲スペーサー領域をマスクとしてウェル領域13の表面層に自己整合的に窒素を注入し熱処理を行う。犠牲スペーサー領域を除去した後に熱酸化を行ってゲート酸化膜21,22を形成する。窒素が注入された部分のシリコンの酸化速度は、窒素が注入されていない部分のシリコンの酸化速度と同じか、それよりも低下する。窒素は、絶縁層20の側壁の犠牲スペーサー領域の下には注入されないので、厚い絶縁層20に接続する部分のゲート酸化膜21の厚さが、それ以外の部分のゲート酸化膜22の厚さと同じか、それよりも厚くなる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル拡散層における不純物濃度プロファイルを急峻で且つ浅接合化することによって短チャネル効果を抑制すると共に、十分な活性化濃度を有する低抵抗なチャネル拡散層によって高駆動力を維持する微細デバイスを実現できるようにする。

【解決手段】MIS型トランジスタは、MIS型の半導体基板100の主面に形成されたゲート絶縁膜101と、該ゲート絶縁膜101の上に形成されたゲート電極102と、半導体基板100におけるゲート電極102の下方に形成されたP型のチャネル拡散層103とを有している。チャネル拡散層103は不純物として炭素を含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】SiO2よりも高い誘電率を有する材料からなる絶縁膜上に設けられた金属電極の仕事関数が所望の値を有する半導体装置を提供することを可能にする。

【解決手段】半導体基板34と、半導体基板上に形成されたトンネル絶縁層36と、トンネル絶縁層上に設けられた浮遊ゲート電極37と、浮遊ゲート電極上に形成され高誘電率材料からなる第1絶縁層38aと、この第1絶縁層上に形成されシリコンおよび酸素ならびに窒素を含むかあるいはシリコンおよび窒素を含む第2絶縁層38bとを有する電極間絶縁膜38と、電極間絶縁膜上に形成された制御ゲート電極40と、第2絶縁層と制御ゲート電極との界面に形成され13族元素を含む界面層44と、制御ゲート電極の両側の半導体基板に形成されたソース・ドレイン領域35と、を含み、界面層の前記13族元素の結合状態数は酸化、窒化、または酸窒化結合状態の総数よりも金属結合状態の数が多い。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

半導体装置の製造方法

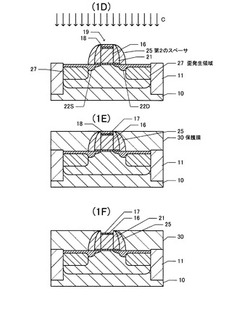

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】超短チャネル化が実現可能であり、閾値を変化させずにON電流を増加させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10と、線状半導体層12が略渦巻き状に成形されてなる渦巻き体13と、線状半導体層12を構成する一対の側壁面部12aに少なくとも形成されてなるゲート絶縁膜14と、ゲート絶縁膜14を介して一対の側壁面部12aに隣接するゲート電極15と、を具備してなり、線状半導体層12に、チャネル領域を含むボディ領域12cと一方のソース・ドレイン領域12dとが設けられるとともに、線状半導体層12のボディ領域12cの下側または線状半導体層12の周囲の半導体基板10に、他方のソース・ドレイン領域12eが設けられ、ボディ領域12cとゲート電極15との間にゲート絶縁膜14が配置されていることを特徴とする半導体装置11を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート長を増加させずにゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11上の絶縁膜12に形成されたゲート形成溝13の内部にゲート絶縁膜16を介してゲート電極17が形成され、前記ゲート電極17の一方側の前記半導体基板11にソース領域14が形成され、他方側の前記半導体基板11にドレイン領域15が形成された半導体装置1において、前記ゲート電極17は、前記ゲート形成溝13内から前記絶縁膜12表面より突出して形成されたゲート電極本体部30と、前記ゲート電極本体部30の前記絶縁膜12表面より突出した部分の側壁に形成された導電性のサイドウォール18とを有することを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】 動作時のオン抵抗を充分に小さくすることが可能な高耐圧のFET及びその製造方法を提供することを目的とする。

【解決手段】 p型GaNチャネル層16がその上下をn型GaNソース層18及びn型GaNドレイン層14によって挟まれた積層構造をメサ形状に加工してその側面に傾斜面を形成し、この傾斜面におけるp型GaNチャネル層16の傾斜した側面上にSiO2 ゲート絶縁膜24を介してゲート電極40Ga、40Gbを設けている。即ち、p型GaNチャネル層16の傾斜した側面をチャネル領域としている。このため、そのチャネル長をp型GaNチャネル層16の厚さによって制御することが可能となり、容易かつ高精度に短チャネル長化を達成することができる。

(もっと読む)

自己整合したソース/ドレイン領域を有するフィン型電界効果トランジスタ・デバイスおよびその形成方法

【課題】改良されたフィン電界効果トランジスタ(FinFET)デバイスと、その製造方法とを提供する。

【解決手段】1つの側面において、電界効果トランジスタ・デバイスを製造する方法は次のステップを含む。その上にシリコン層を有する基板が準備される。そのシリコン層においてフィン・リソグラフィー・ハードマスクがパターニングされる。フィン・リソグラフィー・ハードマスクの中央部分の上にダミー・ゲート構造が置かれる。ダミー・ゲート構造の周りにフィラー層が堆積させられる。フィン・リソグラフィー・ハードマスクの中央部分の上を中心として、フィラー層にトレンチを形成するためにダミー・ゲート構造が除去され、それはデバイスのフィン領域をデバイスのソース領域およびドレイン領域から区別する。フィン領域内のフィン・リソグラフィー・ハードマスクは、シリコン層に複数のフィンをエッチングするために使用される。フィンの上にゲート・スタックを形成するためにトレンチはゲート材料で満たされる。デバイスのソース領域およびドレイン領域を形成するためにフィラー層が除去され、ソース領域およびドレイン領域は無傷であってゲート・スタックと自己整合させられている。

(もっと読む)

101 - 120 / 298

[ Back to top ]