Fターム[5F140BG40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | 研磨、CMP (298)

Fターム[5F140BG40]に分類される特許

21 - 40 / 298

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】縦型PN接合において確実にオン/オフの制御をすることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極とを備える。第1導電型の第1のチャネル領域が、ゲート絶縁膜の下にある半導体層の表面の一部に設けられている。第1導電型とは異なる導電型である第2導電型の拡散層が、第1のチャネル領域のさらに下の半導体層に設けられ、半導体層の表面に対してほぼ垂直方向に第1のチャネル領域の底部と接し、該第1のチャネル領域の底部とPN接合を形成する。第1導電型のドレインおよび第2導電型のソースが、第1のチャネル領域の両側にある半導体層内にそれぞれ設けられている。側壁絶縁膜は、第1のチャネル領域の拡散層側の側面を被覆する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

電界効果トランジスタ、その使用、およびその製造方法

【課題】好適な電界効果トランジスタ、その使用、およびその製造方法を提供すること。

【解決手段】窪み(72)に沿ってドープチャネル領域が配置された半導体基板(10)を有する、縦型電界効果トランジスタが説明される。「埋め込まれた」接続領域(18、54)は、半導体基板(10)の表面に達する。第2の接続領域(16)が、同一の表面の窪みの開口部の近傍内に配置される。好ましくは、分離窪み(70、74、76)が、チャネル領域と導電性配線(54)との間、および電界効果トランジスタと隣接する電気部品との間に製造される。電界効果トランジスタは優れた電気特性を有し、容易に製造される。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

ゲート電極及びその製造方法

【課題】フラットバンド電圧を制御できるとともに、半導体デバイス製造プロセスで使用される高温に曝されても特性の劣化が少ない、nMOSFETのゲート電極を与える。

【解決手段】炭化タンタルにイットリウムを添加した材料でゲート電極を作成する。このゲート電極はイットリウムの添加量に従ってフラットバンド電圧を調節できるとともに、600℃程度の熱処理を受けても特性の劣化が少ない。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

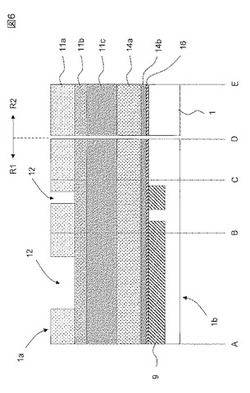

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

21 - 40 / 298

[ Back to top ]