Fターム[5F140BG40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | 研磨、CMP (298)

Fターム[5F140BG40]に分類される特許

61 - 80 / 298

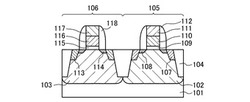

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

基板ドレイン接続を有する横型MOSFET

1つの形式として、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているアクティブゲートを含み、当該ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、横型MOSFETは、ドレイン領域の上に配されている非アクティブゲートをさらに含む。他の形式において、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているゲートを含み、ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、ソース領域及びドレイン領域は第1の導電タイプであって、横型MOSFETは、ソース領域に接しておりかつソース領域の下方にある第2の導電タイプのヘビーボディ領域をさらに含み、ドレイン領域は、ゲートのエッジに近接しているライトドープドレイン(LDD)領域及び単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張しているシンカーを含んでいる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ゲート絶縁膜上のゲート電極の仕事関数を増大させることができ、低い閾値電圧の半導体装置を提供する。

【解決手段】半導体装置1は、基板(シリコン基板2)と、シリコン基板2上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極(Pt含有Ni3Si電極19)を備え、Pt含有Ni3Si電極19が、ゲート絶縁膜4とPt含有Ni3Si電極19との接する部分に、第一金属を含む第一金属シリサイド、および第二金属を含む第二金属シリサイドまたは第二金属を含み、第二金属を含む第二金属シリサイドが、第二金属を含む第二金属シリサイド中のシリコンに対する第二金属の組成比が1より大きい金属リッチシリサイドであることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、短チャネル効果を抑制したままで、オフ電流を増加することなく、オン電流を増大させることが可能な半導体装置(縦型SGT)を提供する。

【解決手段】中空筒状に形成された半導体のボディ部4と、ボディ部4の下部に形成され、ソースおよびドレイン領域の一方となる第1の領域3と、ボディ部4の上部に形成され、ソースおよびドレイン領域の他方となる第2の領域5と、ボディ部4の前記ソース領域と前記ドレイン領域に挟まれた領域に形成されたチャネル領域4aと、チャネル領域4aの内周面および外周面をゲート絶縁膜を介して覆うように形成されたゲート電極7と、第1の領域に接するようにボディ部4の下方に形成され、第1の領域と同じ導電型の半導体層からなる第3の領域3aとを、備えたことを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長を決めるドライエッチングにおいてプラズマ発光をモニターすることによる終点検出方法を用いることにより半導体装置のゲート長を安定して製造する。

【解決手段】ソース拡散層、ドレイン拡散層及び柱状半導体層が基板上に垂直方向に階層的に配置され、柱状半導体層の側壁にゲートが配置される半導体装置の製造方法であって、柱状半導体層を埋め込むように第1の絶縁膜又は導電膜を成膜し、第1の絶縁膜又は導電膜を柱状半導体層上部に形成されたストッパーにより終点検出を行い平坦化し、第2の絶縁膜又は導電膜を成膜し、第2の絶縁膜又は導電膜のエッチングすると共にエッチング時のエッチングレートを算出し、第2の絶縁膜又は導電膜をエッチバックする際の第2の絶縁膜又は導電膜のエッチングレートを用いて第1の絶縁膜又は導電膜のエッチングの終点検出を行うことにより、第1の絶縁膜又は導電膜のエッチング量を制御する。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

61 - 80 / 298

[ Back to top ]