Fターム[5F140BH14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054)

Fターム[5F140BH14]の下位に属するFターム

LDD(Lightly doped dorain−source) (1,105)

GDD(Graded doped dorain) (11)

DDD(Doble doped dorain) (528)

Fターム[5F140BH14]に分類される特許

101 - 120 / 1,410

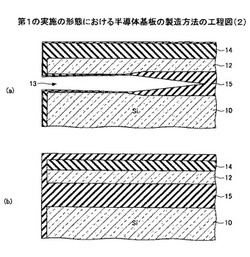

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の特性を劣化させることなく、浅い接合の半導体装置を提供する。

【解決手段】まず、半導体基板上に、ゲート絶縁膜を形成する(s100)。次いで、ゲート絶縁膜上にゲート電極を形成する(s200)。次いで、ゲート電極を形成する工程(s200)の後、第一アニール工程を行う(s300)。次いで、第一アニール工程(s300)の後、ゲート電極の両側における半導体基板に、ポケット領域およびエクステンション領域を構成する不純物注入を行う(s400)。その不純物注入を行う工程(s400)の後、第二アニール工程として、最高アニール温度が1000℃以上で、アニール時間が100ミリ秒以下であるアニールを行う(s700)。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のゲートラスト法の問題点を解決し、さらなる微細化に対応できるゲート構造を実現する。

【解決手段】半導体領域101上から、ダミーゲート構造を除去してリセス107aを形成した後、リセス107aの底部の半導体領域101の表面上に界面層108を形成する。次に、界面層108上及びリセス107aの側壁上に高誘電率絶縁膜109を形成すした後、リセス107a内部の高誘電率絶縁膜109上に、ゲート電極の少なくとも一部となる金属含有膜110を形成する。界面層108上に形成されている部分の高誘電率絶縁膜109の厚さは、リセス107aの側壁上に形成されている部分の高誘電率絶縁膜109の厚さよりも厚い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧調整用金属を含む高誘電率絶縁膜を有するゲート絶縁膜を備えたn型MISトランジスタを有する半導体装置において、ゲート幅が狭くなっても、n型MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】n型MISトランジスタnTrは、半導体基板1における素子分離領域32に囲まれた活性領域1aと、活性領域1a上及び素子分離領域32上に形成され且つ高誘電率絶縁膜12aを有するゲート絶縁膜13aと、ゲート絶縁膜13a上に形成されたゲート電極16aとを備えている。活性領域1aにおける素子分離領域32に接する部分のうち少なくともゲート絶縁膜13aの下側に位置する部分に、n型不純物領域28が形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】新規なDTMOSトランジスタの製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1領域と、第1領域に接続しこれより幅狭の第2領域と、第2領域に接続しこれより幅狭の第3領域とを含む半導体領域の画定工程、半導体領域に第1導電型不純物でウェル領域を形成する工程、ウェル領域上へのゲート絶縁膜形成工程、第3領域を幅方向に横断する第1部と、第1部から第1領域上に延びた第2部とを含むゲート電極を形成する工程、ゲート電極側面に、第2領域の一部を覆い他の一部を露出させるサイドウォールを形成する工程、第1領域及び第2領域の他の一部にゲート電極及びサイドウォールをマスクとし第2導電型不純物を注入する工程、熱処理による第2導電型不純物拡散工程、サイドウォールの一部を薬液で除去する工程、第1領域及び第2領域の他の一部へのシリサイド層形成工程を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

半導体装置の製造方法

【課題】複雑な工程を回避すると共に、高い有効仕事関数値を得ることにより、高歩留まり及び高性能の半導体装置を実現できるようにする。

【解決手段】ダミー電極22をマスクとして、n型活性領域13にp型の不純物イオンを導入することにより、n型活性領域13におけるダミー電極22の両側方にp型のソースドレイン領域25pを形成し、形成されたソースドレイン領域25pに熱処理を施す。熱処理を施した後に、n型活性領域13の上に、ダミー電極22を覆うように層間絶縁膜26を形成し、形成された層間絶縁膜26からダミー電極22を露出し、露出したダミー電極22を除去する。続いて、層間絶縁膜26におけるダミー電極22が除去された凹部26aに、第2の金属電極27を選択的に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】添加元素に起因してNiシリサイド層が高抵抗化することを抑制する。

【解決手段】まず、シリコン層100上に、Niより原子番号が大きい金属元素を含み、Niを含まない反応制御層202を形成する。次いで、反応制御層202上にNiを堆積し、シリコン層100、反応制御層202、及びNiを熱処理することにより、シリコン層100にNiシリサイド層200を形成する。反応制御層202は、Niより原子番号が大きい金属元素から構成されるのが好ましい。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

101 - 120 / 1,410

[ Back to top ]