Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

141 - 160 / 1,105

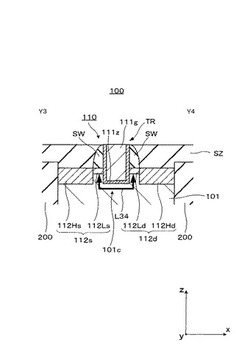

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

MOS型半導体装置

【課題】所望の位置に所望の厚さのゲート酸化膜を有する、高性能かつ長寿命のMOS型半導体を提供すること。

【解決手段】半導体基板と、該半導体基板上にゲート酸化膜を介して形成されたゲート電極とを含み、該ゲート酸化膜の両端部に接するように該半導体基板上にそれぞれ設けられた、該半導体基板の導電型とは異なる導電型の不純物を含む2つの不純物活性領域をそれぞれソース電極及びドレイン電極とする、MOS型半導体装置であって、該ゲート酸化膜を介して形成されたゲート電極は、それぞれが該半導体基板とゲート酸化膜を介して形成された構造を有する複数の領域からなり、各領域の該ゲート酸化膜の厚さが少なくとも2種類の異なる厚さで構成され、該各領域は互いに接合されている、ことを特徴とするMOS型半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

半導体装置

【課題】パワーデバイスとCMOSデバイスとを混載することができ、パワーデバイスのアバランシェ耐量及びESD耐量が高い半導体装置を提供する。

【解決手段】半導体基板11の上部にP型のウェル12を形成し、ウェル12にSTI13を選択的に設け、STI13の開口部14内にSTI13の側面13aに接するようにN+型のソース層17及びドレイン層18を相互に離隔して形成する。また、ソース層17とドレイン層18との間に、P+型のコンタクト層19を形成する。コンタクト層19はソース層17に接し、STI13からは離隔するように形成する。更に、ソース電極21をソース層17及びコンタクト層19に接続し、ドレイン電極22をドレイン層18に接続し、STI13上に側面13aに沿ってゲート電極23を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

141 - 160 / 1,105

[ Back to top ]