Fターム[5F140BK21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739) | 活性化 (1,499)

Fターム[5F140BK21]に分類される特許

201 - 220 / 1,499

半導体装置

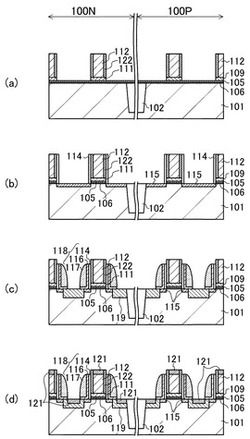

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

MOS型半導体装置およびその製造方法

【課題】ゲートポリ電極とソース及びドレイン高濃度拡散層との間での位置合わせズレを防止し、素子特性や信頼性の均一化を図ることができる。

【解決手段】半導体基板と、前記半導体基板上に形成した酸化膜と、前記半導体基板上に形成した前記酸化膜の除去された領域の寸法に対応して画定したゲート長を有するゲート電極と、前記半導体基板の内部にチャンネル領域を含む位置に配設し、長さは前記酸化膜の幅に対応して決定したオフセット層と、前記オフセット層の内部に配設し、前記ゲート長方向に、前記チャンネル領域から離隔し、前記オフセット層の低濃度不純物より高濃度の不純物を含むソース及びドレイン高濃度不純物拡散層と、前記オフセット層の前記ゲート長方向の両端部に配設し、ソース及びドレイン高濃度拡散層を形成するための不純物のイオン注入に対してのマスクとなる厚さを有する酸化膜とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを半導体基板上に集積する場合に製造コストを低減できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、ディプレッション型電界効果トランジスタの形成予定領域12Daでゲート電極12に開口部32,33を形成する工程と、ゲート電極12をマスクとして、アクティブ領域21に不純物を斜めイオン注入することにより、開口部32,33の下方にゲート電極12の両側の一方から他方にかけて連続的に分布する不純物拡散領域を形成すると同時に、ゲート電極12の両側にそれぞれ不純物拡散領域を形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

窒化物半導体を用いた半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域とゲート電極との位置制御性を向上させ、製造バラツキを低減する。

【解決手段】窒化物半導体を用いた半導体装置10は、窒化物半導体層2に所定間隔を隔てて形成されたソース領域3およびドレイン領域4の間のチャネル領域上に形成され、少なくとも一部がシリサイド合金から形成されたゲート電極6を備え、ソース領域3上にあるゲート電極6の端からゲート電極6と上下に重なるソース領域3の端までの距離L1と、ドレイン領域4上にあるゲート電極6の端からゲート電極6と上下に重なるドレイン領域4の端までの距離L2と、が等しい。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域の寄生抵抗の上昇を抑えつつ短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側にエクステンション領域161を有し、導電型不純物を含むソース・ドレイン領域16と、ソース・ドレイン領域16のエクステンション領域161のゲート電極12側の側面のみに接し、導電型不純物の半導体基板2中での拡散を抑制する性質を有する拡散抑制不純物を含む拡散抑制層15と、を有する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とシリコンの界面抵抗を低く保ちつつ、シリサイド層からの金属元素の拡散を抑制し、リーク電流および寄生抵抗を小さくする。

【解決手段】半導体装置100は、基板1(半導体層)と、基板1に接して形成され、基板1とは逆導電型の半導体電極10と、半導体電極10上に半導体電極10に接して形成されたシリサイド層14と、ゲッタリング層12内部において、基板1と半導体電極10との接合およびシリサイド層14からそれぞれ離れて形成され、シリサイド層14に含まれる金属元素をゲッタリングするゲッタリング層12と、を含む。

(もっと読む)

201 - 220 / 1,499

[ Back to top ]