Fターム[5F140BK25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173) | コンタクトホールの形成 (1,071)

Fターム[5F140BK25]の下位に属するFターム

エッチング (548)

Fターム[5F140BK25]に分類される特許

201 - 220 / 523

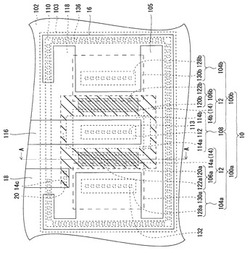

高耐圧MOSトランジスタ装置

【課題】ドレイン配線の幅を従来よりも大きくして、ドレイン配線を導通可能な最大電流量を大きくすること。

【解決手段】高耐圧MOSトランジスタ装置10は、基板102に設けられたPウエル領域103中に形成されており、20V以上のソース−ドレイン間耐圧を有している。そして、Pウエル領域中のソース104a,104b及びドレイン108の間の領域部分が、外部電界の影響を受けて導電型が反転するのを防止する導電性膜を備えている。この導電性膜は、ゲート電極120a,120bと連続的に帯状層12として一体形成されており、基板の表面を平面的に見たとき、帯状層は、ソース及びドレインの一方又は双方を囲んで設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、光吸収膜を利用して実行する新たな製造方法を提供する。

【解決手段】基板上に光吸収膜を堆積し、前記光吸収膜を加工して、第1の膜厚の前記光吸収膜で覆われた第1領域と、前記第1の膜厚よりも薄い第2の膜厚の前記光吸収膜で覆われた第2領域と、前記第2の膜厚よりも薄い第3の膜厚の前記光吸収膜で覆われた第3領域とを形成し、前記基板に光を照射することにより、前記基板をアニールすることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】溝の形状を維持しながらバリを除去するとともに、溝内壁におけるシリコン表面のダメージを除去することが可能な半導体装置の製造方法、及び該製造方法によって製造された半導体装置を提供する。

【解決手段】基板1に埋設領域Mを形成して素子分離を行なう工程と、基板1に溝7a,7b,7cのパターンを形成する工程と、溝7a,7b,7c内壁に保護膜8を形成する工程と、異方性の強い条件でエッチバックすることにより、溝7a,7b,7cのゲート垂直方向側壁7dの一部に保護膜8を残しながら、溝7a,7b,7cのゲート平行方向内壁7eの保護膜8を除去する工程と、保護膜8の除去によってシリコンが露出した領域に水素ベーク処理を行って、溝7a,7b,7cのパターン形成の際に副生されたバリ1a,1aを除去する工程と、を少なくとも有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性を向上させたトレンチ型素子分離構造を有する半導体装置と、その製造方法を提供する。

【解決手段】溝4を第1のシリコン酸化膜6で埋めて熱処理を行い、第1のシリコン酸化膜6上に形成された合わせ目7を第2のシリコン酸化膜8で埋めて再度熱処理を行う。これにより、第1のシリコン酸化膜6及び第2のシリコン酸化膜8を高密度化し、均一なエッチングレートを持つ強固な素子分離酸化膜9として溝4内を充填する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

半導体素子およびその製造方法

【課題】所定の耐圧で、所定のON抵抗を得ることができる実用可能なリサーフ型LDMOSを提供する。

【解決手段】第1導電型不純物の半導体層と、半導体層に形成の局所絶縁層7と、局所絶縁層を挟んで、第2導電型不純物のドレイン層8、ソース層11と、局所絶縁層上からソース層に至る半導体層上のゲート電極13と、を備えた半導体素子において、ドレイン層下、局所絶縁層下、およびゲート電極下の半導体層に、第2導電型不純物をドレイン層より低濃度の低濃度拡散層と、ゲート電極と半導体層の間に、ゲート電極のソース層側端部から局所絶縁層に向かって、局所絶縁層に達することなく延在した第1のゲート絶縁膜と、ゲート電極と半導体層の間に、局所絶縁層の他の側の端部からソース層に向かって延在して第1のゲート絶縁膜に接続された、膜厚が第1のゲート絶縁膜の膜厚より厚く、局所絶縁層の膜厚の半分よりも薄い第2のゲート絶縁膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置

【課題】静電保護回路に従来のsgPMOSトランジスタよりもオン抵抗の小さいsgPMOSトランジスタを配置する。

【解決手段】入出力端子21と接地端子23の間に接続された静電保護回路としてのsgPMOSトランジスタ19を備えている。トランジスタ19はソースとゲートが入出力端子21に接続され、ドレインが接地端子23に接続されている。トランジスタ19のドレインは第1P型ドレイン拡散層5dと第2P型ドレイン拡散層11dからなる二重拡散構造を備えている。ゲート電極17のドレイン側の端部は、第1P型ドレイン拡散層5dの表面にゲート絶縁膜15よりも厚い膜厚で形成されたLOCOS酸化膜13上に乗り上げている。第1P型ドレイン拡散層5dにおける第2P型ドレイン拡散層11d、チャネル9間の距離Yと、第2P型ドレイン拡散層11dと第1P型ドレイン拡散層5dの深さの差Xjとの間にY<Xjの関係が成り立っている。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】トレンチゲート型トランジスタのサブスレショルド特性の向上を図りつつ、ゲートトレンチの幅が縮小された高性能な半導体装置を提供する。

【解決手段】ゲートトレンチ16の底部16bは、STI14から相対的に遠い第1の底部16b1と、STI14から相対的に近い第2の底部16b2を有している。そして、活性領域10aのうち、ゲートトレンチの第2の底部16b2を構成する部分は、側壁チャネル領域10dを構成し、ゲート電極18とSTI14との間に挟まれた薄膜SOI構造を有している。一方、ゲートトレンチの第1の底部16b1を構成する部分は、副チャネル領域10eとして機能する。第2の底部16b2の曲率半径は第1の底部16b1の曲率半径よりも大きい。ゲートトレンチ16の幅方向の略中央部分においては、トレンチの底面が略平坦であるのに対し、幅方向の端部においては、トレンチの底面がほぼ全体的に湾曲している。

(もっと読む)

シリコン含有膜を選択的に堆積する方法

1つの実施形態は、単結晶膜を選択的に堆積するための方法を提供する。この方法は、第1の表面形態を有する第1の表面およびこの第1の表面形態とは異なる第2の表面形態を有する第2の表面を含む基体を準備する工程を含む。シリコン前駆体[108]およびBCl3[134]は相互混合され、これにより供給ガスが形成される。この供給ガスは、化学気相成長条件[122]下でこの基体へ導入される。Si含有層は、供給ガス[120]を導入することにより、第2の表面上に堆積することなく、第1の表面上に選択的に堆積される。 (もっと読む)

半導体装置の製造方法及び半導体装置

【課題】製造コストを抑えつつ、ソース又はドレインと基板との間に生じる接合容量を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1にMOSトランジスタを形成する半導体装置の製造方法であって、シリコン基板1に素子分離膜3を形成する工程と、シリコン基板1上にゲート絶縁膜5を介してゲート電極7を形成する工程と、ゲート電極7と離間して、シリコン基板1上から素子分離膜3上にかけて引出電極9を形成する工程と、ゲート電極7と引出電極9とにより平面視で挟まれた領域のシリコン基板1に不純物を導入してS/D層11を形成する工程と、S/D層11上から引出電極9の少なくとも側面にかけてシリサイド23を形成する工程と、を含む。

(もっと読む)

半導体装置の構造および製造方法

【課題】STI領域の絶縁膜掘り下げにより形成される幅30nm以下の拡散層が配されているFinFETにおいて、寄生抵抗を低減した構造及びその製造方法を提供する。

【解決手段】STI領域105に挟まれ、素子分離領域上方に突き出た幅30nm以下の半導体層にソース及びドレイン領域となる拡散層104が形成されており、ソース及びドレイン領域間のチャネル領域を跨ぐゲート電極を有する凸型Fin構造の電界効果トランジスタであって、前記ソース及びドレイン領域となる拡散層側壁にサイドウォール110b、該サイドウォールに挟まれた拡散層上面に選択エピタキシャル成長シリコン層111、及び該選択エピタキシャル成長シリコン層に接続されるコンタクトプラグ115を有することを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡便な方法で{111}結晶面にトランジスタを形成することが可能な半導体装置を提供する。

【解決手段】 表面が{100}結晶面で構成されたシリコンを有する基板(20)に、活性領域を画定する素子分離絶縁膜(21)が形成されている。この基板に、少なくとも側面の一部が、{111}結晶面が表れた第1の斜面で構成された凹部(36)が形成されている。第1の斜面上に、第1のトランジスタ(TL1)が形成されている。第1のトランジスタは、第1のゲート電極(41b)、第1のソース、及び第1のドレインを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】小型で駆動力が高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1において、シリコン基板2のpMOS領域RpにpMOS8を形成し、nMOS領域RnにnMOS9を形成する。次に、pMOS領域Rpを覆うように、内部に圧縮応力が生じている圧縮応力膜11を形成し、圧縮応力膜11におけるnMOS領域Rn側の端側面上に緩衝膜13を形成し、nMOS領域Rn、圧縮応力膜11の端部、及び緩衝膜13を覆うように、内部に引張応力が生じている引張応力膜12を形成する。緩衝膜13は、その内部応力の大きさが圧縮応力膜11の圧縮応力の大きさ及び引張応力膜12の引張応力の大きさよりも小さい膜とする。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減する。

【解決手段】トレンチ17内には、ゲート酸化膜13Bが形成され、トレンチ17の端部にゲート酸化膜13Bと接してトレンチ酸化膜16が形成されている。トレンチ酸化膜16は、ゲート酸化膜13Bより厚い膜厚を有している。トレンチ17内には、ゲート酸化膜13Bを覆って、ゲート電極18が形成されている。また、N−型半導体層12の表面には、トレンチ17の側壁のゲート酸化膜13Bに接してボディ層19が形成されている。このように、ゲート電極18のトレンチ17の引き出し部18Sに、厚いトレンチ酸化膜16を形成したので、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減することができる。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減する。

【解決手段】N−型半導体層12にトレンチ14を形成する。トレンチ14において、N−型半導体層12のうちトランジスタの活性化領域となる領域には薄いシリコン酸化膜15Bが形成される。一方、活性化領域とならない領域にはシリコン酸化膜15Bよりも厚いシリコン酸化膜15Aが形成される。さらに、トレンチ14内から外に延びる引き出し部16Sがシリコン酸化膜15Aと接するゲート電極16を形成する。これにより、ゲート電極16の引き出し部16Sにおいてゲート電極16とN−型半導体層12の角部12Cとの距離が長く確保されるため、ゲートリーク電流の発生が防止されると共に、ゲート容量を低減することができる。

(もっと読む)

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

DMOSトランジスタ及びその製造方法

【課題】DMOSトランジスタにおいて、斜めイオン注入によりボディ層を形成する際に、リーク電流を低減するとともに、トランジスタのオフ時のソースドレイン間耐圧を向上する。

【解決手段】ホトレジスト層18を形成した後に、ホトレジスト層18及びゲート電極14をマスクとして、A’の矢印で示された第1の方向からゲート電極14の内側の第1のコーナー部14C1を臨んで第1のイオン注入を行う。この第1のイオン注入により、第1のボディ層17A’が形成される。第1のボディ層17A’は第1のコーナー部14C1からゲート電極14の下方に延びて形成され、第1のコーナー部14C1のボディ層17A’のP型不純物濃度を従来例のトランジスタに比して高く確保することができる。

(もっと読む)

201 - 220 / 523

[ Back to top ]