Fターム[5F152NN05]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | SiC (281)

Fターム[5F152NN05]に分類される特許

61 - 80 / 281

炭化珪素基板の製造方法

【課題】炭化珪素基板中を貫通して流体が漏出することを防止することができる炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素から作られた第1および第2の被支持部11、12の各々と、炭化珪素から作られた支持部30とが互いに対向し、かつ第1および第2の被支持部11、12の間に隙間GPが設けられるように、第1および第2の被支持部11、12、および支持部30が配置される。支持部30の炭化珪素を昇華および再結晶させることで、第1および第2の単結晶基板11、12の各々に支持部30が接合される。この際、隙間GPにつながるように支持部30に貫通孔THが形成されることで、隙間GPおよび貫通孔THを通って流体が通過し得る経路PTが形成される。この経路PTを塞ぐことで、炭化珪素基板中を貫通して流体が漏出することを防ぐことが可能となる。

(もっと読む)

炭化珪素基板、半導体装置、炭化珪素基板の製造方法

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板、半導体装置および炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板1は、炭化珪素からなるベース層10と、単結晶炭化珪素からなり、ベース層10上に配置され、ベース層10よりも不可避不純物の濃度が低いSiC層20と、炭化珪素からなり、ベース層10の、SiC層20とは反対側の主面10D上に形成され、ベース層10よりも不可避不純物の濃度が低い被覆層90とを備えている。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝70内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝70内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱することによりSiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝70内に、SiC基板20およびベース基板10とは別の、珪素を含む物質からなる珪素発生源91が配置される。

(もっと読む)

複合基板の製造方法

【課題】窒化物系化合物半導体からなる第1の基板と、第2の基板との接合強度が高い複合基板の製造方法を提供する。

【解決手段】本発明の複合基板の製造方法は、窒化物系化合物半導体からなるバルク基板の表面からイオン注入を行なうステップと、該バルク基板と第2の基板とを貼り合わせることにより貼り合わせ基板を得るステップと、貼り合わせ基板を第1温度まで昇温するステップと、該第1温度を一定時間保持するステップと、該バルク基板の一部である第1の基板が第2の基板上に残るように、バルク基板の他の部分を前記貼り合わせ基板から分離することにより複合基板を生成するステップとを含み、第1温度をT1℃とし、第1の基板の熱膨張係数をA×10-6/℃とし、第2の基板の熱膨張係数をB×10-6/℃とすると、下記式(I)を満たすことを特徴とする。

215≦10(A−B)2−10(A−B)+T1≦410 ・・・(I)

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

(もっと読む)

炭化珪素基板およびその製造方法

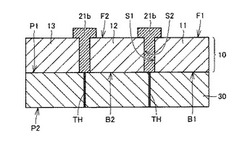

【課題】複数の単結晶層を有する炭化珪素基板中にボイドが形成されることを防止することができる炭化珪素基板およびその製造方法を提供する。

【解決手段】材料基板22の主面M2の第1の領域R1を覆う昇華防止層31が形成される。第1および第2の側面S1、S2によって挟まれた空隙GPが昇華防止層31上に配置されるように、材料基板22上に第1および第2の単結晶層11、12が並べられる。材料基板22と第1および第2の単結晶層11、12とを加熱することによって、主面M2の第2の領域R2から昇華した炭化珪素を、第1の単結晶層11の第1の裏面B1および第2の単結晶層12の第2の裏面B2の各々の上に再結晶させることで、第1および第2の裏面B1、B2の各々と接合したベース基板30が形成される。

(もっと読む)

炭化珪素基板およびその製造方法

【課題】複数の単結晶層を有する炭化珪素基板中にボイドが形成されることを防止することができる炭化珪素基板およびその製造方法を提供する。

【解決手段】材料基板22の主面の第1の領域上に炭素層31が形成される。第1の単結晶層11の第1の裏面B1と、第2の単結晶層12の第2の裏面B2との各々が材料基板22の主面の第2の領域R2に面する部分を有するように、かつ第1の単結晶層11の第1の側面S1と第2の単結晶層12の第2の側面S2とによって挟まれた空隙GPが炭素層31上に配置されるように、第1および第2の単結晶層11、12が材料基板22上に並べられる。材料基板22と第1および第2の単結晶層11、12とを加熱することによって、第1および第2の裏面11、12の各々と接合したベース基板が形成される。

(もっと読む)

単結晶3C−SiC基板の製造方法およびそれによって得られた単結晶3C−SiC基板

【課題】エピタキシャル成長過程において発生する表面欠陥を大幅に減少させることができ、後工程を簡略化しながら半導体デバイスとしての品質を確保できる単結晶3C−SiC基板の製造方法を提供する。

【解決手段】ベース基板上にエピタキシャル成長によって単結晶3C−SiC層を形成させる単結晶3C−SiC基板の製造方法であって、

上記単結晶3C−SiC層を、平坦性の高い表面とその中に点在する表面ピットからなる表面状態となるよう形成する第1の成長段階と、

上記第1の成長段階で得られた単結晶3C−SiC層を、脱離律速の領域において表面の上記表面ピットを埋めるようさらにエピタキシャル成長させる第2の成長段階とを行う。

(もっと読む)

半導体素子用エピタキシャル基板の製造方法、半導体素子用エピタキシャル基板、および半導体素子

【課題】簡便な手法によってエピタキシャル基板の障壁層表面の平坦性を向上させ、ショットキーコンタクト特性の優れたエピタキシャル基板を実現する方法を提供する。

【解決手段】半導体素子用のエピタキシャル基板を製造する方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層をエピタキシャル形成するチャネル層形成工程と、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層をエピタキシャル形成する障壁層形成工程と、障壁層形成工程における加熱温度よりも100℃以上250℃以下高い加熱温度で障壁層が形成された下地基板を加熱することにより、障壁層の表面平坦性を向上させる平坦化処理工程と、を備える。

(もっと読む)

窒化ガリウム系半導体基板の製造方法

【課題】貫通ピットの無い窒化ガリウム系半導体基板を安価に得ることができる窒化ガリウム系半導体基板の製造方法を提供する。

【解決手段】窒化ガリウム系半導体基板の製造方法であって、気相成長装置内に、表面にピット25を生じた窒化ガリウム系半導体層20を有する基板を準備する第1の工程と、前記気相成長装置内で、前記窒化ガリウム系半導体層20上に、非晶質又は多結晶のIII族窒化物のピット埋込層30を形成して前記ピット25を埋める第2の工程と、前記ピット埋込層30を研磨により除去して前記窒化ガリウム系半導体層20の表面を露出させる第3の工程と、を具備する。

(もっと読む)

半導体基板

【課題】単結晶構造を有するSiCから作られた領域と、炭化珪素から作られた支持部とを有し、かつ両者の界面の電気抵抗を低減することができる半導体基板を提供する。

【解決手段】支持部30は炭化珪素から作られている。少なくとも1つの層11の各々は第1および第2の面B1、F1を有する。第1の面B1は支持部30に支持されている。少なくとも1つの層11の各々は第1および第2の領域61、62を有する。第1の領域61は単結晶構造の炭化珪素から作られている。第2の領域62はグラファイトから作られている。第2の面F1は第1の領域61によって形成された面を有する。第1の面B1は、第1の領域61によって形成された面と、第2の領域62によって形成された面との各々を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主表面2Aを有し、炭化珪素からなる基板2と、基板2の主表面2A上にエピタキシャル成長により形成され、炭化珪素からなるp型層4と、p型層4の表面に接触するように形成された酸化膜8とを備えている。そして、p型層4と酸化膜8との界面から10nm以内の領域における窒素原子濃度の最大値は1×1021cm−3以上となっている。

(もっと読む)

イオン・インプラント・アイソレーションによるLED製作

【課題】電気的に隔離された発光ダイオードを提供する。

【解決手段】半導体発光ダイオードは、半導体基板51と、基板上にあるn型III群窒化物のエピタキシャル層52と、n型エピタキシャル層上にあり当該n型層と共にp−n接合部を形成する、III群窒化物のp型エピタキシャル層53と、n型エピタキシャル層上にありp型エピタキシャル層に隣接し、p−n接合部58の一部を電気的に隔離する抵抗性窒化ガリウム領域54とを含む。p型エピタキシャル層上に金属接点層55を形成する。方法の実施形態では、p型エピタキシャル領域上に打ち込みマスクを形成し、p型エピタキシャル領域の部分にイオンを打ち込んでp型エピタキシャル領域の部分を半絶縁性にすることによって、抵抗性窒化ガリウム境界を形成する。フォトレジスト・マスク又は十分に厚い金属層を、打ち込みマスクとして用いることができる。

(もっと読む)

半導体素子、および半導体素子の製造方法

【課題】高移動度と高耐圧を両立し、かつ大電流動作が可能なIII族窒化物半導体を用い

た半導体素子を提供する。

【解決手段】半導体素子は、III族窒化物系化合物半導体からなり、シートキャリア密度

が、1×1012cm−2以上5×1013cm−2以下である半導体動作層と、前記半

導体動作層上に形成された第1の電極及び第2の電極とを備え、前記半導体動作層におけ

る転位密度が1×108cm−2以上、5×108cm−2以下であることを特徴とする

。

(もっと読む)

発光素子および発光素子の製造方法

【課題】本発明は、信頼性が向上し、発光構造物のクラック及びひび割れなどの損傷を防止し、発光効率を向上させる発光素子の製造方法を提供するためのものである。

【解決手段】本発明に従う発光素子の製造方法は、多数のチップ領域及びアイソレーション領域を含む基板の上に多数の化合物半導体層を形成するステップと、前記各チップ領域に発光構造物を形成し、前記アイソレーション領域に緩衝構造物を形成するために前記化合物半導体層をエッチングするステップと、前記発光構造物及び前記緩衝構造物の上に伝導性支持部材を形成するステップと、レーザリフトオフ工程を用いて前記基板を除去するステップと、前記発光構造物を分離するステップと、を含み、前記緩衝構造物は前記発光構造物から離隔する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

半導体複合体構造を形成する方法

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

GaN基板およびその製造方法、GaN層接合基板の製造方法、ならびに半導体デバイスの製造方法

【課題】加工しろが小さく一様な加工が容易なGaN基板およびその製造方法、かかるGaN基板を用いたGaN層接合基板および半導体デバイスの製造方法を提供する。

【解決手段】本GaN基板20は、第1領域20jと、第1領域20jに比べてGa/N組成比が高い第2領域20iとを含み、第2領域20iは、一方の主面20mから所定の深さDを中心に深さD−ΔDから深さD+ΔDまで広がり、深さDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差が、深さD+ΔDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差の3倍であり、第2領域20iのGa/N組成比が、第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比に対して1.05以上である。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

61 - 80 / 281

[ Back to top ]