Fターム[5H007AA03]の内容

Fターム[5H007AA03]に分類される特許

41 - 60 / 263

駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

(もっと読む)

電源回路及び電力変換装置

【課題】本発明はキャリア周波数が増加しても出力電圧の低下を抑える電源回路を提供することである。

【解決手段】直流電力を交流電力に変換し、かつ上アームおよび下アームを構成する複数のスイッチング素子からなるインバータ回路と、前記複数のスイッチング素子を制御する制御回路と、前記制御回路からの信号に基づき、前記複数のスイッチング素子を駆動する駆動回路と、前記駆動回路に電力を供給する絶縁型電源回路と、を有し、前記制御回路は、前記電源回路から前記駆動回路に出力する電源電圧を制御し、前記駆動回路は、キャリア周波数、および前記電源電圧に基づいて前記複数のスイッチング素子を駆動し、前記電源回路は、前記駆動回路に出力された電圧を電源制御ICに出力するフィードバック回路を有し、前記フィードバック回路は前記キャリア周波数の変化に基づいて前記電源制御ICに出力する電圧を制御するダミー回路を有する。

(もっと読む)

電力変換器の制御装置

【課題】デッドタイムの補償電圧の振幅を適切にチューニングすることができる電力変換器の制御装置を提供する。

【解決手段】電力変換器から電動機へ供給される電圧が前記電力変換器に設定されたデッドタイムによって歪むことを抑制するための補償電圧を記憶した記憶手段と、電流理想指令に対応した電圧指令に前記補償電圧を合算した合算電圧指令に基づいて前記電力変換器を制御し、前記合算電圧指令に基づいた前記電動機の駆動力に過不足が生じた場合に、前記電力変換器から前記電動機に流れこむ駆動電流の値を調整することにより、前記駆動力を調整する調整手段と、前記駆動電流の値が調整されたときに前記駆動電流上に発生する電流脈動の値と前記電流理想指令との値の差が所定の基準値よりも小さくなるように、前記補償電圧の振幅を補正する補正手段と、を備えた。

(もっと読む)

半導体素子の駆動装置

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1の半導体素子駆動回路13は、ゲート抵抗21と、電圧源22と、di/dt帰還部23と、バッファ111と、を備えている。バッファ111は、従来良く使われる方式であるトランジスタ111ta,111tbで構成されるIGBT駆動用のバッファ回路の少なくとも一部である。di/dt帰還部23は、トランス121と、抵抗122と、を備えている。即ち、トランス121が、di/dt検出部及びゲイン部に対応する。なお、電圧源22とバッファ111とを結ぶ経路に抵抗122が直列接続され、抵抗122の両端が、トランス121の2次側に接続されており、当該経路上の抵抗122の両端の間が、電圧源に対応する。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】ターンオフ用di/dt帰還部23OFFは、IGBT11Uがターンオフするときに、IGBT11Uのコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。ターンオン用di/dt帰還部23ONは、IGBT11Uがターンオンするときに、FWD12Dの転流電流IFWDに基づいて、帰還電圧VFBを生成する。この場合、ターンオン用di/dt帰還部23ONは、転流電流IFWの方向が、リバースリカバリー区間に対応する方向、即ち図13に示すFWD12Dのカソードからモータ等の負荷L側に流れる方向である場合、帰還電圧VFBを生成し、それ以外の場合、帰還電圧VFBの生成を禁止する。

(もっと読む)

交流電動機の制御装置および制御方法

【課題】インバータを用いた交流電動機制御において、効率を低下させることなくインバータのスイッチングによるサージ電圧を抑制する。

【解決手段】交流制御指令(Vu)とキャリア信号(Vcw)との電圧比較に基づいて、インバータ各相のスイッチング素子のオンオフが制御される。交流制御指令(Vu)は、三相変調のための本来の交流電圧指令(Vu♯)に、3次高調波電圧(Vuh)を重畳することによって得られる。3次高調波電圧(Vuh)は、相電流の特定タイミング(tp1、tp2)を含む所定の電流位相期間(T1)において、当該相でのスイッチング素子のオンオフが固定されるように設定される。

(もっと読む)

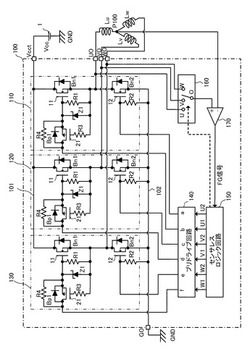

モータ駆動回路

【課題】スイッチング損失が小さく、かつ、安定してモータを動作させることが可能なモータ駆動回路を提供する。

【解決手段】モータ駆動回路1は、インバータ回路2と、制御回路部3と、バッファ回路4a〜4cと、抵抗R2と、キャパシタ素子C1〜C3とを備えている。バッファ回路4aは、PMOSトランジスタQ1aと、NMOSトランジスタQ1bと、抵抗R1aと、抵抗R2aとを有する。バッファ回路4a〜4cにMOSトランジスタを用いるため、ターンオン時間Tonおよびターンオフ時間Toffを短くでき、スイッチング損失を小さくできる。また、MOSトランジスタQ1のゲートをハイに設定する場合は抵抗R2aを介して充電し、ロウに設定する場合は抵抗R2a,R1aを介して放電するため、ターンオフ時間Toffよりターンオン時間Tonが長くなる。そのため、すべての相をオフに設定するデッドタイムを設ける必要がなく、モータを安定して駆動できる。

(もっと読む)

シリーズレギュレータ

【課題】直列に接続した複数のトランジスタの耐圧を確実に分散できるシリーズレギュレータを提供することを課題とする。

【解決手段】複数の出力制御用トランジスタ5a,5bを直列に接続したシリーズレギュレータ5であって、複数の出力制御用トランジスタ5a,5bの耐圧を分散させるための分圧を設定する複数の分圧素子5e,5gと、複数の出力制御用トランジスタ5a,5bにそれぞれ設けられ、出力制御用トランジスタ5a,5bのゲート電圧を制御する分圧制御用トランジスタ5j,5kを備えることを特徴とする。

(もっと読む)

インバータおよびそれを搭載した電力変換装置

【課題】インバータの電力変換効率を向上させる。

【解決手段】インバータ200は、それぞれ電圧が異なる複数の直流電源V1、V2からの直流電力を交流電力に変換する。インバータ200は制御部20を備える。制御部20は、第1の直流電源V1からの電源電圧E1、第2の直流電源V2からの電源電圧E2と、2つの電源電圧の電位差(E1−E2)を用いて擬似正弦波を発生させる。制御部20は、複数の直流電源V1、V2ごとに設けられるHブリッジ回路を制御することで、擬似正弦波を生成する。

(もっと読む)

回転機の制御装置

【課題】モデル予測制御によりスイッチング状態の切替数が増大すること。

【解決手段】現在の操作状態を表現する電圧ベクトルV(n)について、予測電流ベクトルIdqeと指令電流ベクトルIdqrとの誤差ベクトルedqのノルム|edq|が閾値ethよりも大きい場合、この一連の処理を実行する。ここで、現在の操作状態を表現する電圧ベクトルV(n)が有効電圧ベクトルである場合(ステップS34:YES)、平均電圧ベクトルVaとのなす角度が規定角度A(≦20°)以下のものがあるか否かを判断する(ステップS38:YES)。そして、肯定判断される場合、ゼロ電圧ベクトルの優先度が高いとし(ステップS40)、これに関する誤差ベクトルedqのノルム|edq|が閾値eth以下と判断される場合(ステップS42)、ゼロ電圧ベクトルを採用する(ステップS46)。

(もっと読む)

電力変換回路の制御装置

【課題】複数個のチョッパ回路部を備えるマルチフェーズコンバータについて、各チョッパ回路部のコイルを流れる電流の増減周期の出現タイミングを均等化することが困難なこと。

【解決手段】マスタ相の電流の変化速度の反転タイミング間の時間間隔T1を計測する。第m(m=2〜n)のスレーブ相については、マスタ相のコイルを流れる電流がゼロとなるタイミングから、「T1(m−1)/n」だけ遅延したタイミングをコイルを流れる電流がゼロとなる目標タイミングTMに設定する。実際のタイミングT(m)を目標タイミングTMにフィードバック制御すべく、スレーブ相のスイッチング素子のオン時間を操作する。

(もっと読む)

半導体装置

【課題】電流駆動型の半導体装置のゲートへの寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させる。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

(もっと読む)

スイッチング装置

【課題】簡素な構成で、サージ電圧を抑えつつ、リカバリー電流に伴う損失を抑えることができるスイッチング装置を提供する。

【解決手段】モータ制御装置を構成するインバータ回路は、平滑コンデンサと、FETと、スナバ回路とを備えている。スナバ回路は、コンデンサによって構成されている。スナバ回路102を構成するコンデンサ102aの一方の接続点a1から平滑コンデンサ100を経てコンデンサ102aの他方の接続点a2に至る経路r1のインダクタンスLr1が、直列接続されたFET101a、101d、及び、コンデンサ102aによって形成される経路r2のインダクタンスLr2の10倍となるような位置に、コンデンサ102aが接続されている。これにより、従来のように、リカバリー電流を抑える回路を別途設ける必要がなく、簡素な構成で、サージ電圧を抑えつつ、リカバリー電流に伴う損失を抑えることができる。

(もっと読む)

半導体装置

【課題】本発明は、ブートストラップダイオードを備える半導体装置の省エネルギー化ができる半導体装置を提供することを目的とする。

【解決手段】トーテムポール接続された高圧側パワーデバイスと低圧側パワーデバイスの駆動を制御する半導体装置であって、回路負荷を有し、該高圧側パワーデバイスを制御する高圧側駆動回路と、該低圧側パワーデバイスを制御する低圧側駆動回路と、該低圧側駆動回路と接続され該低圧側駆動回路の電源電位であるVCC電位を該低圧側駆動回路に与えるVCC端子と、アノードが該VCC端子と接続されカソードが該高圧側駆動回路と接続され、該高圧側駆動回路の電源電位であるVB電位の充電に用いられるブートストラップダイオードと、該VB電位が該VCC電位よりも小さくなる前に該回路負荷を遮断する手段とを備えたことを特徴とする。

(もっと読む)

ゲート駆動回路の電源装置

【課題】初期充電回路が不要な自己給電形のゲート駆動回路の電源装置を提供することである。

【解決手段】電力用半導体スイッチ素子(3)に並列接続された、スナバダイオード(35)とスナバコンデンサ(37)とからなる直列回路と、端子電圧をゲート駆動回路(11)に電源電圧として印加する電源用コンデンサ(51)と、スナバコンデンサ(37)の正電位側端子と電源用コンデンサの正電位側端子間に介在されて、電源用コンデンサ(51)に充電電流を流すノーマリオンタイプのスイッチ素子(43)と、 ノーマリオンタイプのスイッチ素子(43)を制御するスイッチ制御回路と、を備える。スイッチ制御回路は、電源用コンデンサ(51)の端子電圧が所定値以上になったときにノーマリオンタイプのスイッチ素子(43)をオフさせるように構成される。

(もっと読む)

半導体電力変換装置

【課題】トランジスタ素子のエミッタ−コレクタ間のサージ電圧を確実に収束させることができる半導体電力変換装置を提供する。

【解決手段】半導体電力変換装置1は、IGBT4と、このIGBT4に逆並列に接続されたダイオード5と、IGBT4のゲートに並列に接続されたゲート抵抗8a〜8dと、IGBT4がONからOFFに切り換わる時のIGBT4のエミッタ−コレクタ間のサージ電圧を検出するコレクタ電圧検知回路12と、このコレクタ電圧検知回路12の検出値と基準電圧V1との大小を比較するコンパレータ13と、このコンパレータ13の出力データに応じてカウンタ値をカウントアップまたはカウントダウンさせるカウンタ14と、このカウンタ14のカウンタ値に応じてIGBT4をOFF駆動するためのゲート抵抗8a〜8dを選択する抵抗選択回路15とを備えている。

(もっと読む)

スナバ回路を有する3レベルパルス幅変調インバータ

【課題】単純で低コストの構成によってスイッチング損失を回避可能な回路装置を提供する。

【解決手段】回路装置は、スナバ回路を伴う3レベルパルス幅変調インバータ、陽極・陰極・中央タップ用入力端子、出力端子を有する。インバータは、陽極・陰極用入力端子に接続された外部スイッチング素子、外部端子に接続された内部スイッチング素子を有する。スナバ回路は、コイル、2つのキャパシタ、4つのダイオードを含む直列接続を有する。ダイオードのうち外側の2つは、陽極・陰極用入力端子に直接接続される。内側の2つの間の電気的接続は、一方がコイルを介して中央タップ用入力端子に、他方がインバータの中央橋枝に接続される。キャパシタは、一の端子が直接接続において隣接する内側のダイオードおよび外側のダイオードの1つの間の電気的接続に接続され、他方の端子が外部端子に直接接続される。

(もっと読む)

半導体素子の駆動方法及びその半導体素子を備えた電力変換装置

【課題】トランジスタとダイオードが半導体基板に混在している半導体素子の駆動方法であって、電力損失が抑制される駆動方法を提供すること。

【解決手段】駆動方法は、ダイオードD2を介して還流電流が流れているときに、トランジスタTr2のゲート電極24にゲート電圧Vg(Tr2)を印加するゲート電圧印加工程を備えている。ゲート電圧Vg(Tr2)は、第1電圧VH未満に設定されている。第1電圧VHは、ダイオードD2に逆方向電圧が印加されているときのトンジスタTr2の閾値電圧である。

(もっと読む)

電力変換装置

【課題】電力変換モジュールと接続された積層構造のバスバー組立体において、電力変換モジュールのスイッチングによるサージ電圧を低減できるようにする。

【解決手段】板状の第1、及び第2バスバー(2,3)で絶縁体(4)を挟み込んだバスバー組立体(1)において、第1、及び第2バスバー(2,3)には、第1、及び第2モジュール接続部(2b,3b)から見て、コンデンサ接続部(2c,3c)とは反対方向に、絶縁体(4)を介して互いに対向する所定の領域(A)をそれぞれ設ける。

(もっと読む)

41 - 60 / 263

[ Back to top ]