Fターム[5H740BA11]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563)

Fターム[5H740BA11]の下位に属するFターム

電界効果トランジスタ(FET) (722)

マルチエミッタトランジスタ (26)

Fターム[5H740BA11]に分類される特許

641 - 660 / 815

電力変換装置

【課題】電力変換器のスイッチング素子のゲート、エミッタ端子とゲートドライバの制御信号出力部を結ぶ制御信号配線のインダクタンスを低減し、主回路ノイズの影響を受けにくく、かつ高速制御可能な主回路を有する電力変換装置を提供する。

【解決手段】自己消弧型のスイッチング素子、主回路配線の平板状導体を具備する電力変換装置において、平板状導体の少なくとも1箇所以上に該平板状導体を貫通する穴を設け、該スイッチング素子を制御する信号線を該貫通穴に通して構成する。

(もっと読む)

電気的サージ保護をもたらす取付構造体

取付構造体を用いて、電子素子を電気的サージから保護するための解決策が提供される。具体的には、取付構造体は、導電材料を備え、保護される電気素子に電気的に接続される。導電材料及び/又は取付構造体は、通常動作時には取付構造体が電子素子の動作に悪影響を与えるのを防止するが、電気的サージの間には取付構造体が代替電気経路をもたらすことを可能にする1つ又は複数の特性をもつことができる。 (もっと読む)

コンバータ装置

【課題】PWM整流器の入力側において、最適な回路構成でEMIを低減することができるコンバータ装置を提供する。

【解決手段】PWM整流器4と、PWM整流器4の入力側に第一ACリアクトル3aとを備え交流から直流へ電力変換するコンバータ装置において、第一巻線2aの一端を三相交流電源1のU相に接続し、他端を第一ACリアクトル3aのU相に接続し、第二巻線2bの一端を三相交流電源1のV相に接続し、他端を第一ACリアクトル3aのV相に接続し、第三巻線2cの一端を三相交流電源1のW相に接続し、他端を第一ACリアクトル3aのW相に接続したコモンモードトランス2と、第一ACリアクトル3aの他端各相を用いて中性点NPを作成する中性点作成部3cと、前記中性点NPを前記コモンモードトランス2の第四巻線端2dと接続し、他端を前記PWM整流器4の正側直流母線Pまたは負側直流母線Nのいずれかに接続したものである。

(もっと読む)

電力用半導体素子の駆動装置

【課題】

電圧駆動型半導体素子を含む半導体装置において、どのような特性の半導体素子に対しても特に調整することなく最適な駆動を実現することができる半導体装置を提供すること。

【解決手段】

スイッチング動作における素子状態に応じて変化する電気量の時間変化率を検出し、この検出結果に基づいて、電圧駆動型半導体素子を含む半導体装置を駆動するために、半導体素子のゲートに印加する駆動電圧を半導体素子のスイッチング動作中における複数の素子状態に応じて変化させ、素子の状態の変化のタイミングを複数の素子状態の変化に応じて変化する電流又は電圧に関する電気量の変化率を検出したものに基づいて設定することを特徴とする。

(もっと読む)

電力変換装置とそのサージ電圧抑制方法および風力発電システム

【課題】電圧型PWWインバータが比較的長いケーブルを介して交流電動機や発電機に接続される場合、インダクタンスと静電容量が大きく、サージ電圧や、電圧の時間変化率dV/dtが交流電動機に悪影響を与える。これを、寸法・重量の小さなリアクトルを用いて抑制すること。

【解決手段】電力変換器1の出力端子と発電機または電動機4を結ぶケーブル3に、リアクトル21を接続し、かつ抵抗22とコンデンサ23の直列体を、前記リアクトル21に並列に接続する。また、これらと前記発電機または電動機4との間のケーブル3の各相線間に、コンデンサ24を接続する。

(もっと読む)

駆動制御回路

【課題】部品点数を増加することなく簡単な構成で配線インダクタンスに起因した誤動作を防止することができる駆動制御回路を提供する。

【解決手段】電圧変換部16のグランドラインREがドライブ回路14のグランドラインDEに接続されると共にドライブ回路14のグランドラインDEがパワー素子3のグランド端子PEに接続され、内部電源発生部15のグランドラインGND1から電気的に切り離されている。このため、パワー素子3のスイッチング動作に伴ってパワー素子3のグランド端子PEと内部電源発生部15のグランドラインGND1との間に配線インダクタンスLcに起因して電位差ΔVが発生しても、ドライブ回路14のグランドラインDEとパワー素子3のグランド端子PEとの間に電位差が発生することが抑制され、ドライブ回路14から出力された駆動信号Sdに対し、パワー素子3が誤動作を生じることなく、正常に駆動制御される。

(もっと読む)

電子機器及び電源回路

【課題】インバータ部に印加される制御電圧のレベルを改善してインバータ部のスイッチング損失を減少させる。

【解決手段】本発明は電子装置及び電源回路に関する。本発明による電子装置は、負荷と;前記負荷に駆動電源を供給する電源供給部と;前記駆動電源を断続するインバータ部と;前記インバータ部の一端に印加される基準電圧より低い第1制御電圧と前記基準電圧より高い第2制御電圧とを出力して前記インバータ部を制御する制御電圧提供部とを含む。

(もっと読む)

半導体装置

【課題】半導体スイッチング素子のスイッチングに伴うサージ電圧を吸収するスナバ回路に発生する電圧振動を抑制、半導体素子が破壊されるのを防ぐ。

【解決手段】スナバ回路の発生する電圧を検出し、スイッチングに伴って振動する電圧の位相を検出し、電圧の振動が同位相で重畳されないようにスイッチングのタイミングを制御する。

(もっと読む)

半導体スイッチを制御するための光学的電力供給型駆動回路および方法

【課題】第1の半導体スイッチ(52)を制御するための、光学的電力供給型駆動回路(40)および方法を提供すること。

【解決手段】光学的電力供給型駆動回路(40)は、光ファイバケーブル(14)から第1の光信号に応答して第1の電圧を出力するように構成された光電池(100)と、光電池(100)に電気的に結合され、第1の電圧から受け取った電気エネルギーを蓄積し、第2の電圧を出力するように構成されたエネルギー蓄積デバイス(102)を含む。光学的電力供給型駆動回路(40)は、光電池(100)およびエネルギー蓄積デバイス(102)の両方に電気的に結合された電気回路をさらに含む。電気回路は、第2の電圧によって付勢される。電気回路は、第1の半導体スイッチ(52)の動作を制御するために、第1の電圧を受け取り、第1の電圧に応答して第3の電圧を出力する。

(もっと読む)

電源装置及び電源供給方法

【課題】本発明は、スイッチング素子のスイッチング時のサージと損失の低減を両立させることができる電源装置及び電源供給方法の提供を目的とする。

【解決手段】スイッチング素子の電源を供給するにあたり、スイッチング素子の検出温度が閾値以下であるか否かを定期的に監視し(ステップ1)、検出温度が所定の閾値以下でないときにはスイッチング素子の電源電圧を制限せず(ステップ2)、検出温度が所定の閾値以下のときにはスイッチング素子の電源電圧を制限する(ステップ3)ことにより、スイッチング素子の耐圧が低い低温時にスイッチング素子に供給される電源電圧を下げて低温時でのサージ発生による耐圧超えを防ぐとともに、耐圧特性が低温時に比して高い常温時の耐圧に基づいて決定された小さなゲート抵抗値を用いてスイッチング損失を低減させる。

(もっと読む)

高調波抑制装置

【課題】入力電流検出手段や高速な演算装置が不要であり、低コストにて実現可能な高調波抑制装置を提供する。

【解決手段】多相入力の交流直接変換器の入力フィルタとして用いられる高調波抑制装置において、電源1と交流直接変換器3との間の各相にそれぞれ直列に接続されたリアクトル21と、リアクトル21と交流直接変換器3との間において、各相間にそれぞれ接続された1個以上のコンデンサ23と、電源1とリアクトル21との間において、各相間にそれぞれ接続された1個以上の直列回路とを備え、前記直列回路を、抵抗24とコンデンサ25とを直列に接続して構成する。

(もっと読む)

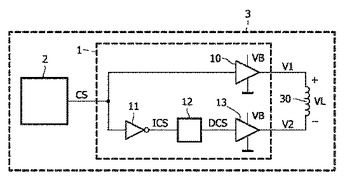

誘導性負荷駆動装置

駆動装置(1)は、誘導性負荷(30)に出力電圧(VL)を供給する。この駆動装置は、予め決定した範囲内の制御可能なデューティサイクルを有するパルス幅変調制御信号(CS)を受ける入力端を有している。第1のスイッチ回路(10)は、第1のスイッチ信号(CS;ICS)を受けて第1の電圧(V1)を生じ、第2のスイッチ回路(13)は、第2のスイッチ信号(DCS;CSD)を受けて第2の電圧(V2)を生じ、第1の電圧(V1)と第2の電圧(V2)との差を前記出力電圧(VL)とする。インバータ(11;15)及び遅延回路(12;16)は制御信号(CS)を受け、互いに反転し遅延した第1のスイッチ信号(CS;ICS)及び第2のスイッチ信号(DCS;CSD)を生じる。遅延回路(12;16)の遅延時間(dT)は、予め決定した範囲内の前記制御可能なデューティサイクルの各々に対して、単一の極性を有する出力電圧が得られるように選択する。  (もっと読む)

(もっと読む)

ノイズ低減フィルタ

【課題】 ノイズ低減性能の向上とフィルタの小型化、低コスト化を実現したノイズ低減フィルタを得る。

【解決手段】 この発明のノイズ低減フィルタは、複数の電力供給線と接地線との間に挿入された第1の静電容量要素3と、供給電力を任意の周波数成分の交流電力に変換して負荷に供給する電力変換装置11のノイズを低減するノイズ低減装置10と前記第1の静電容量要素との間に設けられた第1のインピーダンス要素4と、を備え、

第1のインピーダンス要素4により、ノイズ低減装置10によるノイズ低減効果と第1の静電容量要素3によるノイズ低減効果を両立できるようにした。

(もっと読む)

高電圧配電および高電圧送電の分野における電流変換のための装置および電力用半導体ユニットの負荷変動ストレスの低減のための方法

電力用半導体ユニットからなる直列接続回路を持った少なくとも1つの電力変換器弁(2a,2b)と、電力用半導体ユニットの冷却のための冷却手段(3,4,5,7)とを有する高電圧配電および高電圧送電の分野における電流変換のための装置(1)において、電力用半導体ユニットの温度行程を低コストにて減少させ得る装置(1)を提供するために、冷却手段(3,4,5,7)が電力用半導体ユニットを介する電流の流れに依存した冷却をもたらす制御手段を持つことを提案する。  (もっと読む)

(もっと読む)

インバータ回路装置

【課題】低圧側回路から高圧側回路に制御信号を伝達する昇圧レベルシフト回路を有するインバータ装置で、駆動信号を上アームの半導体スイッチング素子のゲートに確実に伝達する。

【解決手段】本発明のインバータ装置は、低圧側回路から高圧側回路に制御信号を伝達する昇圧レベルシフト回路を備え、セット、リセットパルスの幅を、半導体スイッチング素子に逆並列に接続したダイオードのリカバリ電流のピーク値から電圧振動が収まるまでの時間より長く設定し、ロジックフィルタの動作によって信号が遮断されていても、信号を上アームに確実に伝える。

(もっと読む)

電力変換装置

【課題】オフサージ電圧の上昇を抑制しつつ、従来よりもターンオフ損失を低減させることができる電力変換装置を提供する。

【解決手段】IGBTをスイッチング素子として用いる電力変換装置において、ゲートの外部抵抗の大きさを変化させた場合、外部抵抗の大きさを20Ωから9Ωまで小さくしたときでは、ターンオフ損失が減少し、かつ、オフサージ電圧が増加し、外部抵抗の大きさを9Ωから2Ωまで小さくしたとき、ターンオフ損失が減少し、かつ、オフサージ電圧が減少するという特性をIGBTが有している場合、外部抵抗の大きさを2Ω以上9Ω未満に設定する。これにより、外部抵抗の大きさを9Ω以上に設定する場合と比較して、IGBTのターンオフ時において、ダイナミックアバランシェ現象を多く発生させることができ、その結果、オフサージ電圧の上昇を抑制しつつ、従来よりもターンオフ損失を低減させることができる。

(もっと読む)

電力変換装置

【課題】電力変換装置のスナバ回路の小形化、簡略化を行いつつ、逆変換部の素子のスイッチング損失の低減をすることにより、装置の小形化などを実現する技術、製品を供給することを課題とする。

【解決手段】逆変換部のP相、N相と、平滑コンデンサの正極、または負極とを接続したバスバーと直列接続されたコンデンサの中間層を接続する配線バスバーの形状を大きくし、互いに重なり合う面積を大きくして、流れる電流を互いに逆方向とすることで、インダクタンスを低減する。

(もっと読む)

電圧駆動型半導体素子のゲート駆動回路及びこれを用いた電力変換装置

【課題】各アームに電圧駆動型半導体素子が複数個直列接続された電力変換装置の回路構成において、光ファイバケーブルなどの制御信号線の本数が直列数に比例して増加するのを防止する。

【解決手段】各アームに電圧駆動型半導体素子Q1〜Q4がn個直列接続された電力変換装置において、各電圧駆動型半導体素子にはゲート駆動回路をそれぞれ備え、電圧駆動型半導体素子とゲート駆動回路を接続するゲート線をそれぞれ互いに磁気結合回路5〜7により磁気結合し、m段目(m=1〜nの整数)以外のゲート駆動回路に、この磁気結合に基づいて発生する電圧を検出する電圧検出回路9、10、19と、前記電圧検出回路からの検出結果に応じてオンオフ信号を出力するホールド回路12、13、22を接続し、m段目のゲート駆動回路に制御回路18からのオンオフ信号を入力する。

(もっと読む)

電圧駆動形スイッチング素子のゲート駆動回路

【課題】

IGBTのスイッチング時間,損失の増加を抑えながら、IGBTのスイッチング時のdi/dt,dv/dtを抑制する。

【解決手段】

IGBTを含む電圧駆動形スイッチングデバイスのスイッチング動作を制御する信号を増幅する駆動手段と、前記IGBTのゲート電圧を検出する手段と、前記駆動手段のオン(オフ)時の出力電圧を時間経過に伴って徐々に降下(上昇)させる電圧降下(上昇)手段と、前記出力電圧を徐々に上昇させる電圧上昇(降下)手段とを設け、前記IGBTのゲート電圧の検出値に応じて前記電圧下降(上昇)手段から前記電圧上昇(降下)手段への切換えを行うことにより、IGBTのオン(オフ)時のdi/dt,dv/dtを抑制する。

(もっと読む)

ブートコンデンサの充電方法

【課題】直流電圧の低下を抑えつつ、各相のブートコンデンサの駆動電圧のバラツキを低減させる充電方法を提供する。

【解決手段】絶縁ゲート型バイポーラトランジスタ41に対して直列に接続されたハイアーム側スイッチング素子の動作を制御するNPN型トランジスタ42と、NPN型トランジスタ42に対して動作電源を与えるブートコンデンサ32と、を有するUVW相が設けられたインバータにおいて、第1ステップでは、絶縁ゲート型バイポーラトランジスタ41及びNPN型トランジスタ42が、前置充電期間にNPN型トランジスタ42をオフ状態に維持して、絶縁ゲート型バイポーラトランジスタ41を介して電源回路30によってブートコンデンサ32等を充電し、第2ステップではUVWの各相のブートコンデンサそれぞれに対して、第1ステップによって行う充電を1〜20パルスずつ割り当てて行い、第3ステップでは、第2ステップを繰り返す。

(もっと読む)

641 - 660 / 815

[ Back to top ]