Fターム[5J022BA01]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 高精度化 (1,223)

Fターム[5J022BA01]の下位に属するFターム

雑音の除去 (254)

オフセット・ドリフトの除去 (306)

非線形歪みの除去 (345)

Fターム[5J022BA01]に分類される特許

1 - 20 / 318

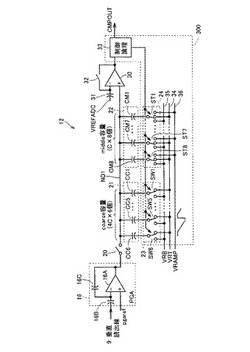

固体撮像装置

【課題】従来よりも高精度かつ高速の変換が可能なカラムADCを内蔵した固体撮像装置を提供する。

【解決手段】固体撮像装置200において、各変換部12は、対応の垂直読出線9を介して出力された各画素の信号を第1〜第N(Nは3以上の整数)の変換ステージを順に実行することによってデジタル値に変換する。第1〜第N−1の変換ステージでは、各変換部12は、画素の信号を保持する保持ノードND1の電圧を所定の電圧ステップずつ変化させながら参照電圧と比較することによって、デジタル値の最上位ビットを含む上位の複数ビットの値を決定する。第Nの変換ステージでは、各変換部12は、第N−1の変換ステージにおける電圧ステップの範囲またはそれを超える範囲で、保持ノードND1の電圧を連続的に変化させながら参照電圧と比較することによって、残りの最下位ビットまでの値を決定する。

(もっと読む)

AD変換器、光電変換装置、および撮像システム

【課題】 並列型AD変換器におけるカウンター回路の動作を精度良く制御する。

【解決手段】 第1クロック信号を計数してカウント信号を出力するカウンター回路と、第1クロック信号に基づいて、第2クロック信号を生成する第2クロック信号生成部と、カウント開始信号を前記第2クロック信号に同期して出力するクロック同期化部と、を有し、カウンター回路は、第2クロックに同期したカウント開始信号に応じて計数を行う。

(もっと読む)

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

AD変換回路および撮像装置

【課題】カウントした計数値の誤差の発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ104から出力される上位用カウントクロックに基づいてカウントを行って第2の上位計数値を取得する。変更部103は、上位カウンタ101のカウントクロックの切換えの際に、カウントクロックの論理状態を所定の状態に変更する。

(もっと読む)

A/D変換器、固体撮像装置および電子情報機器

【課題】入射光の光強度をディジタル信号値に変換するのに要する時間を、得られるディジタル信号値が大きな誤差を含むのを回避しつつ短縮することができるA/D変換器を実現する。

【解決手段】固体撮像装置100を構成するA/D変換器120において、一定値ずつ変化するディジタル値を出力するカウンタ124と、該ディジタル値の二乗と該ディジタル値の和に比例させてランプ電圧を発生する二次ランプ発生回路123と、アナログ入力電圧と該ランプ電圧とを比較して大小関係の反転時を検出する比較回路121と、該比較回路121が該反転時を検出したとき、該カウンタから得られる時間情報から、該アナログ入力電圧の平方根を変換して得られるディジタル変換値を取り出すラッチ122とを備え、該アナログ入力電圧の平方根を該ディジタル変換値に変換する。

(もっと読む)

固体撮像装置

【課題】画素数の増大に伴うバッファの数の増大、微細化に伴うプロセスばらつきの増大により、このクロック信号のデューティ比の崩れを抑制する。

【解決手段】固体撮像装置1は、複数の画素10がアレイ状に配置された画素部20と、少なくとも一つのアナログデジタル変換部30を含む第1グループおよび第2グループを有する変換部と、直列に接続された第1のクロックバッファおよび第2のクロックバッファを有するクロック供給部とを含み、第1グループおよび第2グループのアナログデジタル変換部のそれぞれは、比較部およびカウンタ部を有し、第1のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して、第1グループのカウンタ部のそれぞれと第2のクロックバッファに出力し、第2のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して第2グループのカウンタ部のそれぞれに出力する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

リングオシュレータ回路、A/D変換回路、および固体撮像装置

【課題】偶数個(段)の反転回路をリング状に連結した構成でも、安定した発振動作を行うリングオシュレータ回路、これを用いたA/D変換回路、およびこれを用いた固体撮像装置を提供する。

【解決手段】反転回路が偶数個リング状に連結された円周上でパルス信号を周回させるリングオシュレータ回路であって、反転回路の内の一つが、制御信号に応じて第1のパルス信号を駆動する第1の起動用反転回路であり、他の一つが、第1のパルス信号の先頭エッジに基づいて第2のパルス信号を駆動する第2の起動用反転回路であり、さらに他の一つが、第2のパルス信号を駆動後の第1のパルス信号の先頭エッジに基づいて第3のパルス信号を駆動する第3の起動用反転回路であり、第1〜第3のパルス信号が円周上に同時に存在するとき、パルス信号の進行方向に対して第3、第2、第1の順になるように、第1〜第3の起動用反転回路を反転回路の円周内に配置する。

(もっと読む)

量子化装置

【課題】 回路規模の増加を抑制しつつ、複数ビットの量子化信号を生成する。

【解決手段】 量子化装置は、第1クロックの1周期前の量子化信号に基づく量子化誤差と第1信号とに基づいて、第2信号を生成する信号処理部と、第1クロックより高速の第2クロックに同期して動作し、第2信号を第1クロックの1周期以内に量子化し、量子化信号を生成する量子化部とを有している。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

光センサおよびそれを備えた携帯電話ならびにデジタルカメラ

【課題】低照度から高照度までの入力に対してリニアな出力を得ることが可能であるとともに、フォトダイオードの出力電流の温度依存性を補正することができる光センサを実現する。

【解決手段】光センサ(1)において、第1のアナログ−デジタル変換回路(11)に、第1のフォトダイオード(PD1)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第1の基準電流源が備えられ、第2のアナログ−デジタル変換回路(12)に、第2のフォトダイオード(PD2)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第2の基準電流源が備えられ、第1の基準電流源を用いて出力された第1の検出結果(ADCOUT1)と、第2の基準電流源を用いて出力された第2の検出結果(ADCOUT1)とから、第2のフォトダイオード(12)による可視波長域の受光強度を検出することによって照度を測定する。

(もっと読む)

V−F変換装置

【課題】汎用のV−F変換器を用いて広い周波数帯域においても高精度なパルスカウントができるV−F変換装置を提供する。

【解決手段】入力する信号量に応じたアナログ電圧値を出力するアナログ電圧出力回路1と、アナログ電圧出力回路1が出力するアナログ電圧値を周波数に変換して周波数に応じたパルスを出力する複数のV−F変換器21a、21b、・・・21nと、該複数のV−F変換器から入力する複数のパルスをフィルタリングし、このフィルタリングされたパルスの数をカウントする演算手段31とを備える。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

電圧発生回路、共振回路、通信装置、通信システム、ワイヤレス充電システム、電源装置、及び、電子機器

【課題】 可変容量素子の容量を制御するための制御電圧を発生する電圧発生回路において、より簡易で、かつ、より低価格な構成を提供する。

【解決手段】 電圧発生回路3を、抵抗回20と、複数の入力ポート11〜18と、出力ポート30とで構成する。抵抗回路20は、複数の抵抗21〜27を有し、複数の抵抗21〜27を直列又は並列に接続して構成される。複数の入力ポート11〜18には、電位状態をハイ状態、ロー状態及び開放状態のいずれかに制御する制御信号がそれぞれ入力される。そして、出力ポート30は、複数の入力ポート11〜18のそれぞれの電位状態の組み合わせに対応した電圧値の電圧信号Vcを出力する。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】見かけ上の容量比精度を高めて変換精度を向上できるD/A変換回路、及びこれを含むA/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードNCに接続される第1のD/A変換部DAC1と、出力ノードNCと第1のノードN1との間に設けられる第1の直列キャパシターCS1と、第1のノードN1に接続される第2のD/A変換部DAC2と、制御回路20を含む。第1のD/A変換部DAC1は第1のキャパシターアレイ部CAR1と第1のスイッチアレイ部SAR1を含む。第2のD/A変換部DAC2は第2のキャパシターアレイ部CAR2と第2のスイッチアレイ部SAR2を含む。制御回路20は、入力デジタルデータの各ビットに対するキャパシターの割り当てを動的に変化させるスイッチ制御を第1のD/A変換部DAC1の第1のスイッチアレイ部SAR1に対して行う。

(もっと読む)

サンプル・ホールド回路、回路装置、A/D変換回路及び電子機器

【課題】チャージインジェクションによる信号誤差を抑制できるサンプル・ホールド回路、回路装置、A/D変換回路及び電子機器を提供すること。

【解決手段】サンプル・ホールド回路は、一端が第1のノードN1に接続されるサンプリング用キャパシターCsと、第1のノードN1と第2のノードN2の間に設けられるメイントランジスターTMと、メイントランジスターTMと並列に設けられるサブトランジスターTSと、を含む。サブトランジスターTSのゲート面積は、メイントランジスターTMのゲート面積よりも小さい。サンプリング期間からホールド期間への切り替わりにおいて、メイントランジスターTMがオフになった後にサブトランジスターTSがオフになる。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

デジタルアナログ変換装置およびその制御方法

【課題】処理負荷の増大を抑制しつつ、アナログ信号の出力レベルの精度を向上させる。

【解決手段】本発明のデジタルアナログ変換装置は、Nビットのデジタル信号をアナログ信号に変換して出力するDAコンバータと、所定のサンプリング周期で入力されるM(M>N)ビットのデジタル信号に示される第1の値を、Nビットのデジタル信号で示される範囲内の第2の値となるように所定比で縮小して出力するスケール変換部と、第2の値をNビットのデジタル信号で示される第3の値に変換して出力するビット長変換部と、所定のサンプリング周期内で、第2の値と第3の値との誤差を示す第4の値を入力値とする所定の演算を複数回行い、演算結果が0である場合には第3の値を、演算結果が正である場合には、第3の値から1を減算した第5の値を、演算結果が負である場合には、第3の値に1を加算した第6の値を、DAコンバータに出力する出力値決定部と、を有する。

(もっと読む)

A/D変換器

【課題】より一層の高精度化が可能なA/D変換器を提供する。

【解決手段】制御回路(制御手段)5は、積分器1において入力電圧Vinを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第1の二重積分と第1の基準電圧(グラウンド電圧)VAGNDを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第2の二重積分とが選択的に行われるように入力切替部2を制御する機能を有する。第1の二重積分における第2積分期間に対応したカウント値からなる第1のカウント値と第2の二重積分における第2積分期間に対応したカウント値からなる第2のカウント値とが入力されるディジタル回路7を備える。ディジタル回路7は、第1のカウント値ごとに、第1のカウント値の前後1つずつの第2のカウント値の平均値を第1のカウント値から減算した差分値を求めてディジタル値として出力する機能を有する。

(もっと読む)

A/D変換器

【課題】従来の四重積分型A/D変換器に比べて、精度の低下を防止しつつ単位時間当たりの変換回数を増やすことが可能なA/D変換器を提供する。

【解決手段】積分器1において入力電圧Vinを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第1の二重積分と第1の基準電圧(グラウンド電圧)VAGNDを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第2の二重積分とが選択的に行われる。ディジタル回路7は、第1の二重積分における第2積分期間に対応した第1のカウント値を被減数、第2の二重積分における第2積分期間に対応した第2のカウント値を減数として被減数から減数を減算して得た差分値をディジタル値として出力する機能を有し、差分値を求めるにあたり、第2のカウント値を時系列で入力される2つの第1のカウント値に対する減数として共用する。

(もっと読む)

1 - 20 / 318

[ Back to top ]