Fターム[5J039JJ18]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180)

Fターム[5J039JJ18]の下位に属するFターム

比較結果が2端子に生じるもの (5)

デジタル出力 (138)

Fターム[5J039JJ18]に分類される特許

1 - 20 / 37

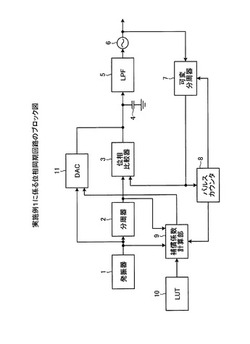

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

中波放送機の発振部

【課題】2台の水晶発振器を備え、一方の水晶発振器が出力する周波数信号を利用して発振する中波放送機の発振部において、2台の水晶発振器各々の発振器の出力周波数のズレを監視し、ズレが発見された場合に、アラーム信号を発生し、迅速な対応を即すことで、中波放送機の信頼性をより高める。

【解決手段】現用と予備の2台の水晶発振器の出力周波数を、常に比較若しくは監視し、周波数ズレが発生した場合に対応できるように発振制御を行う中波放送機の発振部とした。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

衛星ナビゲーションシステムのためのマスタークロック生成装置

【課題】低廉な製作コスト及び部品コストで製造することができ、更に、マスタータイミング基準信号をより高精度で生成することのできる衛星ナビゲーションシステムのためのマスタークロック生成装置の提供。

【解決手段】複数の周波数信号入力部の各々に、原子時計信号から成る第1参照周波数信号と、原子時計信号から成る第2参照周波数信号との、いずれか一方を供給する。複数の周波数コンバータ(110、115、120、125)は、互いに同一周波数の中間周波数信号を出力する。スイッチングマトリクス130は、前記中間周波数信号のうちの1つを主クロックとして選択して送出すると共に、別の1つを副クロックとして選択して送出する。周波数信号生成器150は、前記主クロックから基準周波数信号を生成し、複数の周波数信号出力部へ送出する。位相メーター170は、前記主クロックと前記副クロックとの間の位相差を測定し、異常挙動を検出する。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

1 - 20 / 37

[ Back to top ]