Fターム[5J042CA21]の内容

Fターム[5J042CA21]の下位に属するFターム

Fターム[5J042CA21]に分類される特許

1 - 20 / 33

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

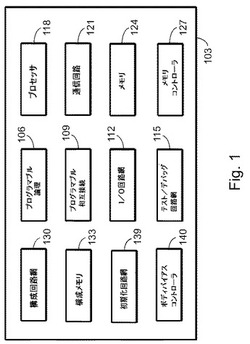

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

熱論理演算素子、熱論理演算回路および熱論理演算方法

【課題】熱を入力として熱を出力とする論理演算素子を提供する。

【解決手段】熱論理演算素子として、スピン軌道相互作用を用いて熱電変換を行う少なくとも2つの熱電変換素子と、構成する論理ゲートに対応させて個々の熱電変換素子の起電力取出し領域を少なくとも抵抗発熱体を介して接続した伝導路とを有して、その少なくとも2つの熱電変換素子の各々への熱入力を入力とすると共に、伝導路の抵抗発熱体から得られる熱を出力として、論理ゲートとして動作させる。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源遮断後の起動時間が短く、高集積化及び低消費電力化を図ることが可能であるプログラマブルロジックデバイスを提供する。

【解決手段】入出力ブロックと、論理エレメントを有する複数の論理ブロックと、該複数の論理ブロックを接続する配線とを有するプログラマブルロジックデバイスにおいて、論理エレメントは、コンフィギュレーションデータが保持されたコンフィギュレーションメモリ及び選択回路を有するルックアップテーブルを有する。また、コンフィギュレーションメモリは、酸化物半導体膜をチャネル領域に有するトランジスタと、該トランジスタ及び選択回路の間に設けられた演算回路とを有するメモリ素子を複数有し、入力信号に応じて選択回路によりコンフィギュレーションデータを選択的に切り替えて出力する。

(もっと読む)

プログラマブルデバイスを過電圧攻撃から守るためのシステムおよび方法

【課題】レジスタ、過電圧検出回路およびロジック回路を有しているプログラマブル集積回路デバイスを提供すること。

【解決手段】少なくとも1ビットの値を格納するように構成されているレジスタであって、該レジスタは、印加された電圧源に結合されている、レジスタと、過電圧検出回路であって、該過電圧検出回路は、該印加された電圧源によって発生された電圧を検出することと、検出された電圧がトリガー電圧よりも高いか、または等しい場合に、過電圧信号を生成することとを行うように構成されている、過電圧検出回路と、ロジック回路であって、該ロジック回路は、該生成された過電圧信号に応答して、該レジスタをクリアにするように構成されている、ロジック回路とを含む、プログラマブル集積回路デバイス。

(もっと読む)

論理回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)を高くし、消費電力を低減する。

【解決手段】論理回路は、ゲート10,11が入力端子3,4に接続され、ドレイン12が出力端子5に接続され、ソース13がグランド端子8に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子6に接続されたインプレーンダブルゲートトランジスター2とを備える。

(もっと読む)

演算装置

【課題】より小さな規模で論理回路が構成できるようにする。

【解決手段】第1周波数に第1差分周波数を加えた第1入力周波数の第1振動および第1周波数から第1差分周波数を減じた第2入力周波数の第2振動が入力される第1入力部101と、第1周波数と異なる周波数の第2周波数に第2差分周波数を加えた第3入力周波数の第3振動および第2周波数から第2差分周波数を減じた第4入力周波数の第4振動が選択的に入力される第2入力部102と、第1入力部101の振動と第2入力部102の振動との差を出力する周波数変換部103と、設定された少なくとも第1設定周波数を検出して対応する第1出力を出力する周波数検出部104とを少なくとも備える。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

IP機能ブロックのフレキシブルな配置のためのPLDアーキテクチャ

【課題】ベース信号のルーティングアーキテクチャを最適にするようにIP機能ブロックを配置できるPLDアーキテクチャを提供すること。

【解決手段】本発明のプログラム可能な論理デバイス(PLD)は、アレイに構成された複数の論理素子(LE)と、LE間に信号をルーティングするための複数の信号ルーティング線を備えるベース信号のルーティングアーキテクチャと、を備え、LEのアレイ内にはホールが形成され、ホールは、周辺部分および中央部分によって特徴付けられ、ベース信号のルーティングアーキテクチャは、ホールにおいて少なくとも部分的に中断され、PLDは、ホールの周辺部分内にインターフェース回路をさらに備え、インターフェース回路は、ホール内の回路を信号をルーティングするアーキテクチャに結合するように構成可能であり、PLDは、該ホール内にIP機能ブロックをさらに備え、インターフェース回路に電気的に結合される。

(もっと読む)

プログラマブル論理回路、半導体集積回路装置、情報処理システムおよび制御プログラム

【課題】効率的に消費電力を低減して省エネルギー性を向上させることのできるプログラマブル論理回路を提供する。

【解決手段】外部からのアクセスによりその論理演算処理が変更可能な複数の論理ブロック(1a〜1i)と、該論理ブロックの間の接続を外部からのアクセスにより変更可能な配線領域2と、各論理ブロック毎に電源をオン・オフ可能なオン・オフ手段(電源オン・オフ部3)と、システムの動作モードに対応させた動作データを導入する導入手段(動作データ導入部5)と、導入された動作データに基づいて指定された論理ブロックの電源をオン・オフさせる制御手段(オン・オフ制御部4)と、電源がオンされた論理ブロックについて、配線領域における各論理ブロック間の配線状態を動作データに含まれる回路データに基づいて変更する配線変更手段(配線変更部6)とを少なくとも備える。

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

集積回路における故障耐性

【課題】 集積回路内の故障耐性を定めるシステム及び方法を提供する。

【解決手段】 集積回路内の故障耐性を定めるシステムは、集積回路によって保持されるプログラム可能論理デバイスを含むことができる。本システムはまた、プログラム可能論理デバイスによって保持される設定可能メモリを含んで、プログラム可能論理デバイスの一部分の機能及び/又は接続を制御することができる。本システムは、プログラム可能論理デバイスにより保持され、ユーザ及び/又は設定可能メモリと通信するユーザ論理をさらに含むことができる。ユーザ論理は、ユーザ要求の変化に基づいて設定可能メモリ内の破損データを識別することができる。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

半導体集積回路

【課題】機能を柔軟に制御可能なアナログの機能ICを提供する。

【解決手段】アナログブロック10は、所定のアナログ信号処理を実行する。デジタルブロック20は、再構成可能に構成され、所定のデジタル信号処理を実行してアナログブロック10を制御する。FeRAM30は、デジタルブロック20の回路構成のコンフィギュレーションデータを格納する。機能IC100は、FeRAM混載プロセスを用いてひとつの半導体基板上に一体集積化され、アナログブロック10の動作状態が、デジタルブロック20の構成状態に応じて変更可能である。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置のロジック領域に冗長救済を行う構成を提供することを目的とする。

【解決手段】本発明の1つの実施の形態は、ロジック領域2を有する半導体装置1である。そして、当該半導体装置1は、ロジック領域2内に設けられる同一の構成を有する複数の基本セル21と、複数の基本セル21と同一の構成を有する冗長セル22と、複数の基本セル21及び冗長セル22のそれぞれに入力される信号を切り替える入力セレクタ23と、基本セル21及び冗長セル22のそれぞれから出力される信号を切り替える出力セレクタ24とを備えている。さらに、当該半導体装置1は、入力セレクタ23及び出力セレクタ24のうち少なくとも一方を切り替えて、冗長セル22を機能させ複数の基本セル21のうち故障したセルを救済する。

(もっと読む)

半導体装置およびその駆動方法

【課題】集積回路内に多数形成され、論理回路などを構成するMOSFETから成る半導体素子1において、高機能化を図る。

【解決手段】ウェル2内にソース領域3とドレイン領域4とが形成され、かつそれらの領域間のチャネル領域5上に、ゲート絶縁膜6を介してゲート電極7が形成されるMOSFETにおいて、たとえばSOI基板を用い、かつフィールド酸化膜などによって各素子間を電気的に絶縁し、各素子毎にソース領域3およびドレイン領域4以外の領域で層間絶縁膜にコンタクト孔を形成し、チャネル領域5から基板端子TWを引出す。これによって、ゲート端子TGと該基板端子TWとの2つを入力とする2入力1出力の素子を実現することができ、論理回路などを構成するにあたって、集積度を向上し、高速化および低コスト化を図ることができる。

(もっと読む)

論理回路装置

【課題】本発明は、1クロックサイクル内に複数回の異なる論理演算が可能な論理回路装置を提供することを目的とする。

【解決手段】再構成可能な論理回路装置は、論理構成を動的に再構成可能な複数の論理ブロックと、複数の論理ブロック間を動的再構成可能に接続するネットワークとを含み、複数の論理ブロックのうちの少なくとも1つの論理ブロックは、第1のデータ信号と第1のデータ信号の有効時にアサート状態となる第1の有効指示信号とを入力として受け取り、第1のデータ信号を入力とする第1の論理演算により生成された第2のデータ信号と第2のデータ信号の有効時にアサート状態となる第2の有効指示信号とを出力として生成し、第1の有効指示信号のアサート状態に応答して第2のデータ信号をアサート状態に設定する基本論理演算素子を含むことを特徴とする。

(もっと読む)

半導体集積回路装置及びその半導体集積回路装置を備えるストレージ装置

【解決課題】第1の大規模集積回路動作中に論理ブロックの不良を検出しても、停止することなく動作を継続する。

【解決手段】半導体集積回路装置は、複数の1の論理ブロックを有する第1の大規模集積回路と、第1の大規模集積回路に接続するとともに第2の論理ブロックを有する書換え可能な第2の大規模集積回路と、複数の第1の論理ブロックで実行される用途を実現するためのデータを保存するメモリと、第1の大規模集積回路の動作中に第1の論理ブロックの不良を検出した場合に、前第2の論理ブロックに不良を検出した第1の論理ブロックと対応するメモリに保存されたデータを書き込み、不良を検出した第1の論理ブロックの代替として第2の論理ブロックを使用する制御を行なう制御部とを備える。

(もっと読む)

半導体集積回路装置およびその駆動方法

【課題】複数の演算部に対して、降圧回路を用いることなく、簡単に電源分割することができる半導体集積回路装置およびその駆動方法を提供する。

【解決手段】半導体集積回路装置は、電源端VDDCと接地端GNCとの間に直列に接続され、データを処理する複数の演算部ICA、ICBと、処理すべきデータを受け取り、複数の演算部のそれぞれの作業負荷が等しくなるように、データを複数の演算部のそれぞれへ割り振るコントローラCTLとを備えた。

(もっと読む)

論理関数を実行する電気デバイス

電子デバイスが少なくとも1の論理関数を実行するために示されている。デバイスは、電子取出器に連結された電子放出式の電極配列を具える。電極配列は、光電陰極と、陽極と、光電陰極と陽極の間に規定され、キャビティのわきに配列された1又はそれ以上のゲートとを具える少なくとも1の基本ユニットを具える。1又はそれ以上のゲートは電圧電源ユニットに接続可能であり、1又はそれ以上の論理値のそれぞれに対応する1又はそれ以上の入力電圧信号によって動作する。陽極は、得られる論理関数の指標であるデバイスの電気出力が読み出される浮遊電極として機能する。陽極は、同じデバイスの別の陰極陽極ユニットの光電陰極に電気的に接続される、又は別の電子デバイスの電極に接続される。 (もっと読む)

プログラマブル論理回路

【課題】配線の複雑化なく、短時間かつ容易に、論理の再構成を行う。

【解決手段】本発明の例に関わるプログラマブル論理回路は、第1の電源ノードN1と出力ノードO1との間に接続され、磁気固着層と磁気記録層の磁化方向の相対関係に応じてコンダクタンスが変化する第1のトランジスタSPと、第2の電源ノードN2と出力ノードO1との間に接続され、第1のトランジスタSPのコンダクタンスの最大値と最小値との間の値にコンダクタンスが設定される第2のトランジスタSNと、第3の電源ノードN3と出力ノードO1との間に直列接続される第3のトランジスタT1及び抵抗素子R1とを備える。入力信号A,Bを与え、かつ、第1及び第3の電源ノードN1,N2の間にスピン注入電流を流している状態で、出力ノードO1に出力される出力信号Yの検証を行う。

(もっと読む)

1 - 20 / 33

[ Back to top ]